50

STP2002QFP

Sun Microelectronics

Fast Ethernet, Parallel Port, SCSI (FEPS) - STP2002QFP

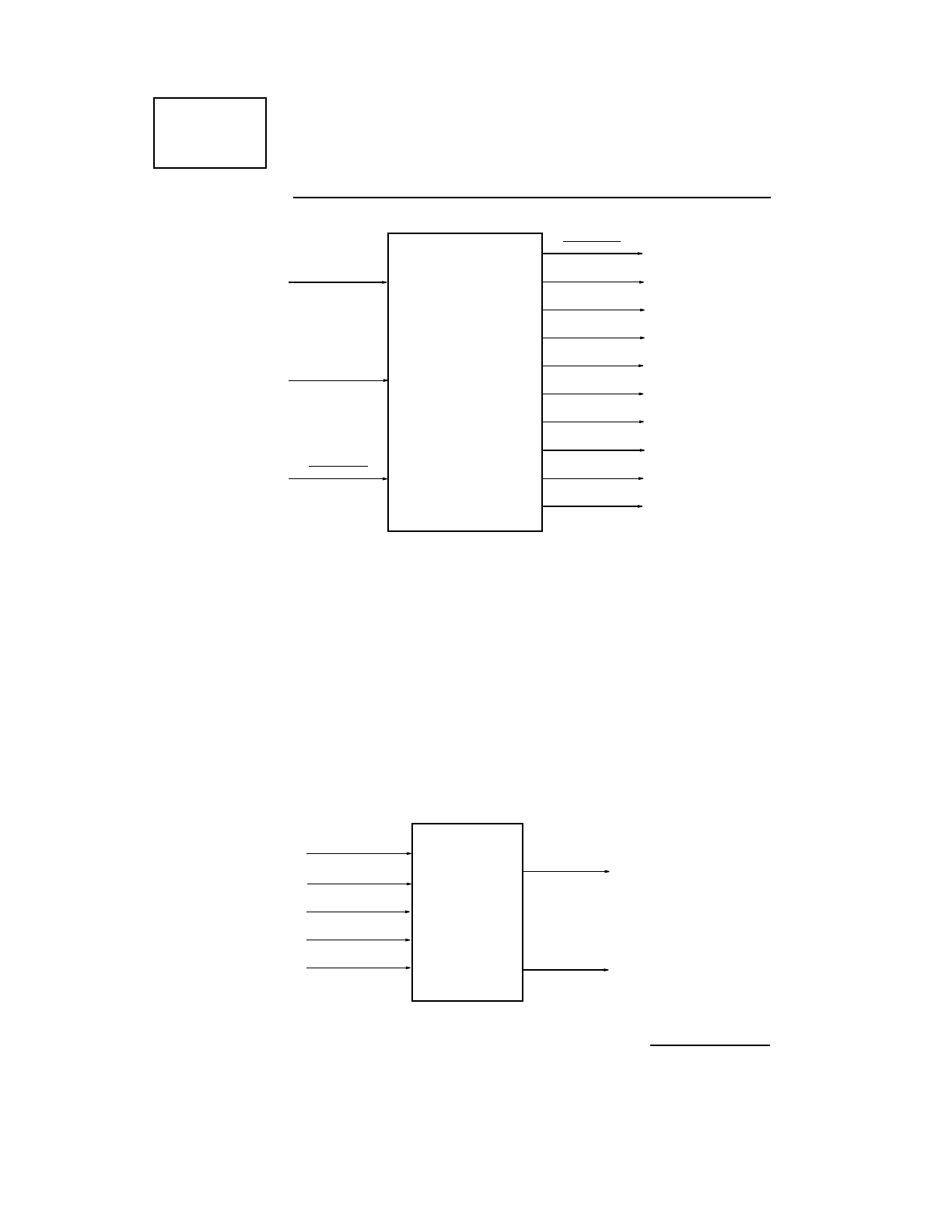

Figure 15.

6.2.2 Instruction Register

The instruction register is used to select the test to be performed and/or the

test data register to be accessed. The FEPS instruction register is four bits

wide and is a shift register with parallel load and parallel outputs. At the start

of an instruction register shift cycle (during the CAPTURE-IR state), the least

two significant bits are loaded with 01 pattern. During the TEST-LOGIC-RE-

SET controller state the instruction register must have the IDCODE. The in-

struction register state is updated at the falling edge of the JTAG_TCK. The

shifting of the instruction register occurs at each rising edge of JTAG_TCK.

DR_CLOCK

DR_UPDATE

DR_SHIFT

IR_CLOCK

IR_SHIFT

JTAG_TDO_EN

REG_SEL

TAP_RESET

DR_CAPTURE

IR_UPDATE

JTAG_TCK

JTAG_TMS

JTAG_TRST

JTAG_TAP

IR-CLOCK

IR_SHIFT

JTAG_TDI

IR_UPDATE

TAP_RESET

IR_TDO

IR_VALUE[3:0]

JTAG_JR