63

STP2002QFP

Fast Ethernet, Parallel Port, SCSI (FEPS) - STP2002QFP

Sun Microsystems,

7.2.3 Byte Count Register

This register is implemented as a 24-bit down counter. When reading this reg-

ister as a word, bits 31:24 will read as 0s. The register should be loaded with

a 24-bit byte count which, if enabled via the P_EN_CNT bit in the P_CSR,

will be decremented every time a byte is transferred between the FEPS and

whatever external device is connected to the parallel port. During a transition

of this register from 1 to 0, the terminal count signal (P_TC), will generate an

interrupt if not disabled via the P_TCI_DIS bit of the P_CSR.

If the P_EN_NEXT bit in the P_CSR is set, then a write to the P_BCNT

register will write to the P_NEXT_BCNT register instead. Whenever the

P_NEXT_ADDR register is copied into the P_ADDR register, the

P_NEXT_BCNT register is copied into the P_BCNT register at the same

time. If P_NEXT_ADDR is being copied in P_ADDR and P_NEXT_BCNT

has not been written since the last time P_NEXT_BCNT was copied in

P_BCNT, the last value that was written into P_NEXT_BCNT will again be

copied into P_BCNT. This provides a shortcut in setting up consecutive

DMA transfers of equal size from different addresses, in that

P_NEXT_BCNT only needs to be written once as long as P_NEXT_ADDR

is loaded for each successive transfer. If P_EN_NEXT is not set when

P_BCNT expires (changes from 0x000001 to 0x000000), then parallel port

DMA activity will be stopped and the P_DMA_ON bit will read as 0 until

P_ADDR is written. If P_EN_NEXT is set, then DMA will be stopped on

P_BCNT expiration.

Note: Loading P_BCNT with 0 will allow 2**24 bytes to be trans-

ferred before it expires.

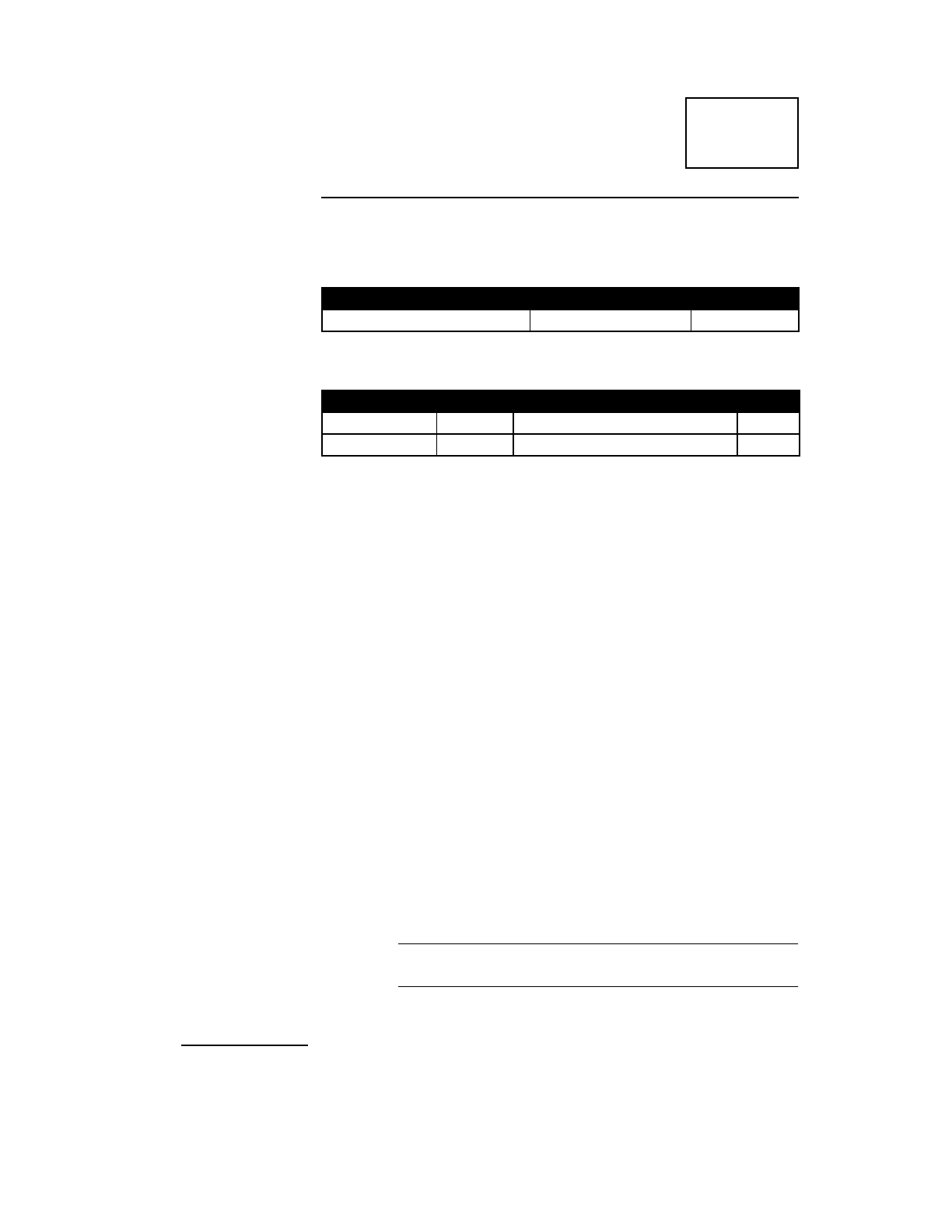

Table 23: Byte Count Register Address

Register Physical Address Access Size

Byte count register (P_BCNT) 0xC80_0008 4 bytes

Table 24: Byte Count Register Definition

Field Bits Description Type

P_BCNT 23:0 DMA byte count register R/W

P_NEXT_BCNT 23:0 Next DMA byte count register W