110 AMD Geode™ SC1200/SC1201 Processor Data Book

SuperI/O Module

32579B

5.5.2.9 Interrupt Handling

The RTC has a single Interrupt Request line which handles

the following three interrupt conditions:

• Periodic interrupt.

• Alarm interrupt.

• Update end interrupt.

The interrupts are generated if the respective enable bits in

the CRB register are set prior to an interrupt event occur-

rence. Reading the CRC register clears all interrupt flags.

Thus, when multiple interrupts are enabled, the interrupt

service routine should first read and store the CRC regis-

ter, and then deal with all pending interrupts by referring to

this stored status.

If an interrupt is not serviced before a second occurrence

of the same interrupt condition, the second interrupt event

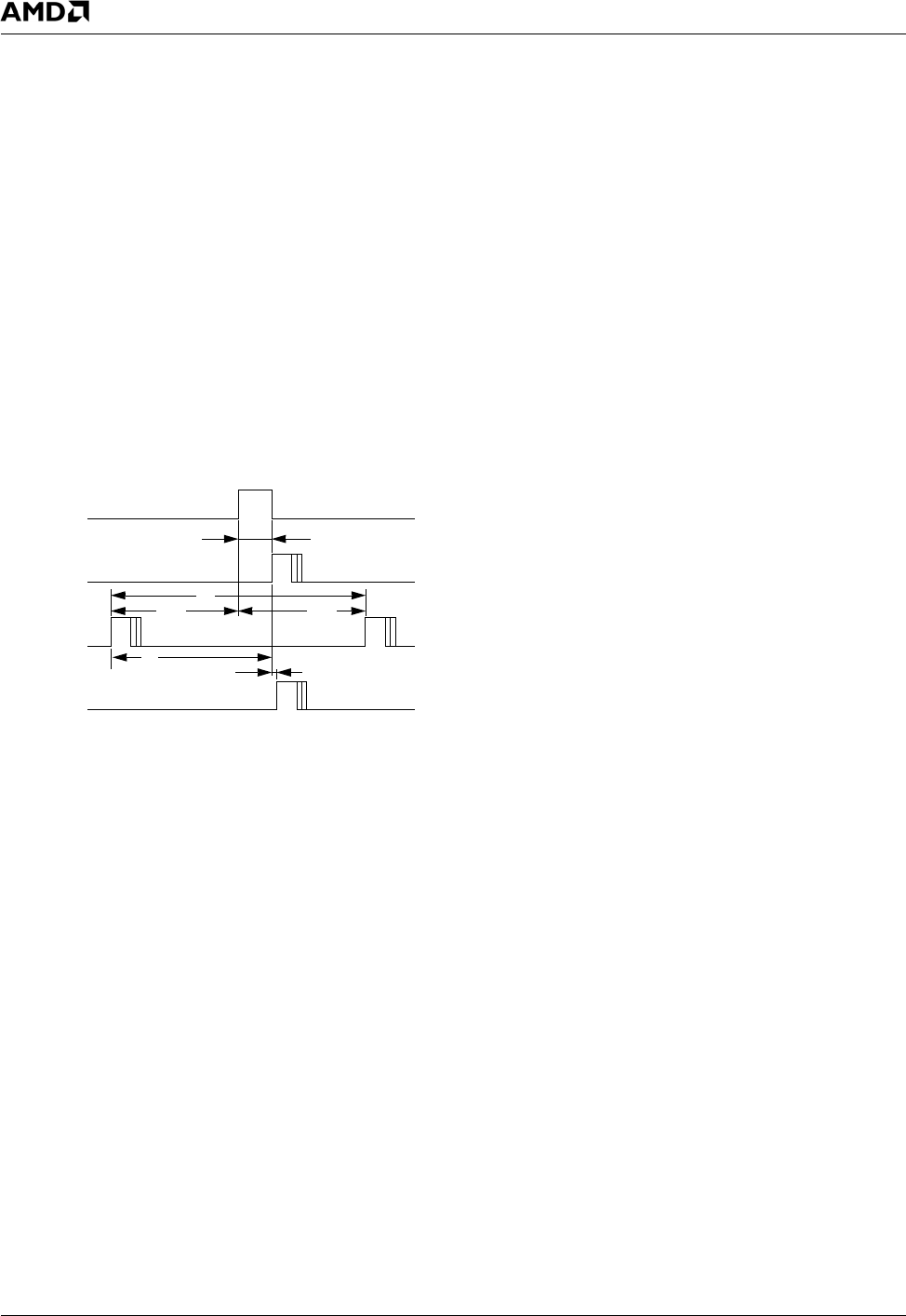

is lost. Figure 5-12 illustrates the interrupt timing in the

RTC.

Figure 5-12. Interrupt/Status Timing

5.5.2.10 Battery-Backed RAMs and Registers

The RTC has two battery-backed RAMs and 17 registers,

used by the logical units themselves. Battery-backup power

enables information retention during system power down.

The RAMs are:

• Standard RAM

• Extended RAM

The memory maps and register content of the RAMs is

provided in Section 5.5.4 "RTC General-Purpose RAM

Map" on page 115.

The first 14 bytes and 3 programmable bytes of the Stan-

dard RAM are overlaid by time, alarm data and control reg-

isters. The remaining 111 bytes are general-purpose

memory.

Registers with reserved bits should be written using the

read-modify-write method.

All register locations within the device are accessed by the

RTC Index and Data registers (at base address and base

address+1). The Index register points to the register loca-

tion being accessed, and the Data register contains the

data to be transferred to or from the location. An additional

128 bytes of battery-backed RAM (also called Extended

RAM) may be accessed via a second pair of Index and

Data registers.

Access to the two RAMs may be locked. For details see

Table 5-7 on page 99.

244 μs

Bit 7

Bit 4

Bit 6

Bit 5

A

C

of CRA

of CRC

of CRC

of CRC

P/2 P/2

30.5 μs

B

P

Flags (and IRQ) are reset at the conclusion of CRC read or by

reset.

A =Update In Progress bit high before update occurs = 244 μs

B =Periodic interrupt to update = Period (periodic int) / 2 +

244 μs

C =Update to Alarm Interrupt = 30.5 μs

P =Period is programmed by RS[3:0] of CRA