AMD Geode™ SC1200/SC1201 Processor Data Book 349

Video Processor Module - Video Processor Registers - Function 4

32579B

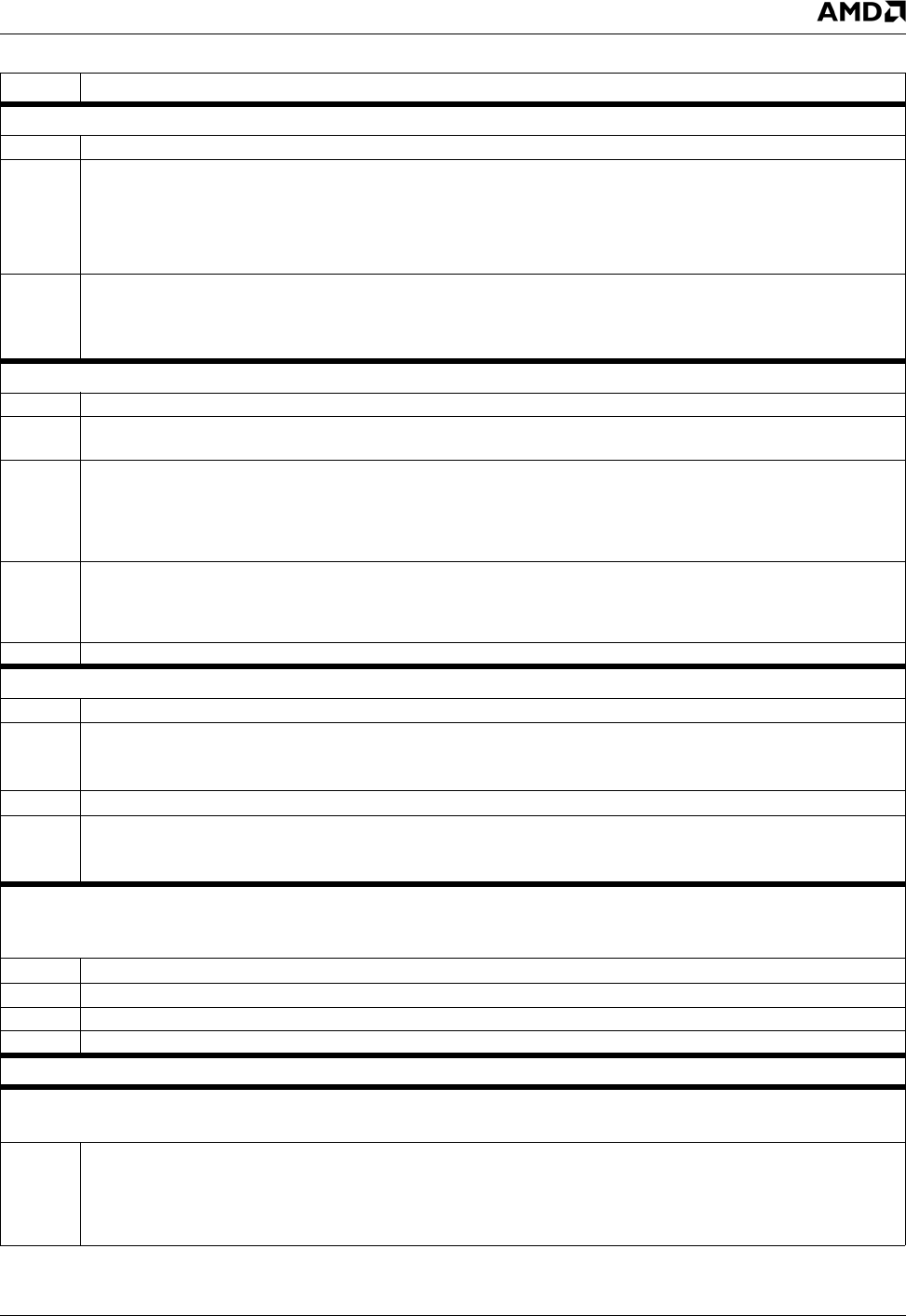

Offset 88h-8Bh Alpha Window 3 Color Register (R/W) Reset Value: 00000000h

31:25 Reserved.

24 ALPHA3_COLOR_REG_EN (Alpha Window 3 Color Register Enable). Enable bit for the color key matching in Alpha

Window 3.

0: Disable. Where there is a color key match, graphics and video are alpha-blended.

1: Enable. If this bit is enabled and the alpha window is enabled, then where there is a color key match, the color value (in

bits [23:0], ALPHA3_COLOR_REG) is displayed.

23:0 ALPHA3_COLOR_REG (Alpha Window 3 Color Register). Specifies the color to be displayed inside Alpha Window 3

when there is a color key match in the alpha window. This is an RGB value (for RGB blending) or a YUV value (for YUV

blending). In Interlaced YUV blending mode, Y/2 value should be used.

This color is only displayed if the alpha window is enabled and the bit 24 (ALPHA3_COLOR_REG_EN) is enabled.

Offset 8Ch-8Fh Alpha Window 3 Control Register (R/W) Reset Value: 00000000h

31:18 Reserved.

17 LOAD_ALPHA (Load Alpha Value). (Write Only) When set to 1, this bit causes the Video Processor to load the alpha

value (in bits [7:0], ALPHA3_VAL) at the start of the next frame.

16 ALPHA3_WIN_EN (Alpha Window 3 Enable). Enable bit for Alpha Window 3.

0: Disable Alpha Window 3.

1: Enable Alpha Window 3.

Valid only if video window is enabled (F4BAR0+Memory Offset 00h[0] = 1)

15:8 ALPHA3_INCR (Alpha Window 3 Increment). Specifies the alpha value increment/decrement. This is a signed 8-bit value

that is added to the alpha value for each frame. The MSB (bit 15) indicates the sign (i.e., increment or decrement). When

this value reaches either the maximum or the minimum alpha value (255 or 0) it keeps that value (i.e., it is not incremented/

decremented) until it is reloaded via bit 17 (LOAD_ALPHA).

7:0 ALPHA3_VAL (Alpha Window 3 Value). Specifies the alpha value to be used for this window.

Offset 90h-93h Video Request Register (R/W) Reset Value: 001B0017h

31:28 Reserved. Set to 0.

27:16 VIDEO_X_REQ (Video Horizontal Request). Determines the horizontal (pixel) location at which to start requesting video

data out of the video FIFO. This value is calculated according to the following formula:

Value = Desired screen position + (H_TOTAL – H_SYNC_END) – 2.

15:11 Reserved.

10:0 VIDEO_Y_REQ (Video Vertical Request). Determines the line number at which to start requesting video data out of the

video FIFO. This value is calculated according to the following formula:

Value = Desired screen position + (V_TOTAL – V_SYNC_END) + 1.

Offset 94h-97h Alpha Watch Register (RO) Reset Value: 00000000h

Alpha values may be automatically incremented/decremented for successive frames. This register can be used to read the alpha values

that are being used in the current frame.

31:24 Reserved.

23:16 ALPHA3_VAL (Value for Alpha Window 3).

15:8 ALPHA2_VAL (Value for Alpha Window 2).

7:0 ALPHA1_VAL (Value for Alpha Window 1).

Offset 98h-3FFh Reserved

Offset 400h-403h Video Processor Display Mode Register (R/W) Reset Value: 00000000h

Selects various Video Processor modes.

31 Video FIFO Underflow (Empty).

0: No underflow has occurred.

1: Underflow has occurred.

Write 1 to reset this bit.

Table 7-9. F4BAR0+Memory Offset: Video Processor Configuration Registers (Continued)

Bit Description