AMD Geode™ SC1200/SC1201 Processor Data Book 315

Video Processor Module

32579B

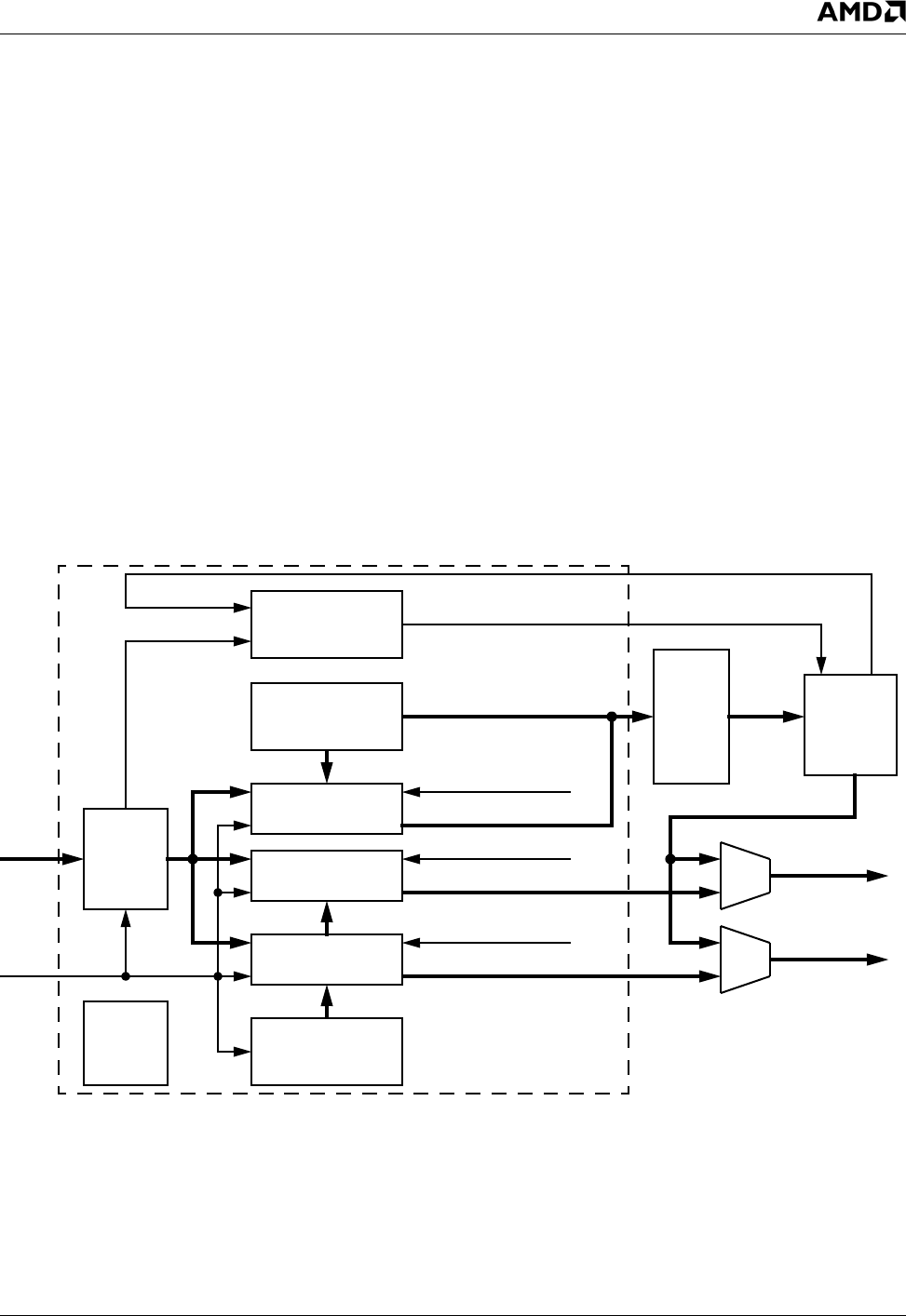

7.2.1 Video Input Port (VIP)

The VIP block is designed to interface the SC1200/SC1201

processor with external video processors (e.g., Philips

PNX1300 or Sigma Designs EM8400) or external TV

decoders (e.g., Philips SAA7114). It inputs CCIR-656

Video and raw VBI data sourced by those devices,

decodes the data, and delivers the data directly to the

Video Formatter (Direct Video/VBI modes) or to the GX1

module’s Video Frame Buffer (Capture Video/VBI modes).

Figure 7-4 shows a diagram of the VIP block.

From the VIP block’s perspective, Direct Video/VBI modes

are always on. There are no registers that enable/disable

Direct Video/VBI modes. The data source selected at the

video mux (F4BAR0+Memory Offset 400h[1:0]) and VBI

mux (F4BAR0+Memory Offset 400h[2]) determine if the

data from the VIP interface is moved directly or must be

captured.

Three FIFOs in the VIP block support the efficient move-

ment of Video and VBI data. For Capture Video/VBI

modes, a 128-byte FIFO buffers both Video and raw VBI

data processed by the CCIR-656 decoder. For Direct

Video/VBI modes, there are two FIFOs that buffer the

CCIR-656 decoder’s data. A 2048-byte FIFO buffers Video

data and a 128-byte FIFO buffers VBI data. The FIFOs are

also used to provide clock domain changes. The VIP inter-

face clock (nominally 27 MHz) is the input clock domain for

all three FIFOs. For the Capture Video/VBI FIFO, the data

is clocked out using the FPCI clock (33 or 66 MHz). For the

Direct Video FIFO, the Video data is clocked out using the

GX1’s Video port clock (75, 116, or 133 MHz GX1 core

clock divided by 2 or 4) and for the Direct VBI FIFO the

data is clocked out with the GX1’s pixel port clock (approxi-

mately 27 MHz only because VBI out is only supported for

TVs).

Since the VIP block treats Video data and VBI data inde-

pendently, this means that they can operate in Capture

Video/VBI or Direct Video/VBI modes independent of each

other, with some restrictions. Table 7-1 on page 316 shows

the supported Direct/Capture configurations.

Figure 7-4. VIP Block Diagram

CCIR-656

Decoder

Capture Video/VBI

Direct Video

Direct VBI

Capture Video/VBI

Controller and

Capture Video/VBI Data

Fast-PCI Clock

Bus Master

FIFO

FIFO

FIFO

Fast

X-Bus

to

Fast-PCI

Bridge

GX1

Module

Fast-PCI

Direct Video/VBI

Controller

VIP

Data

VIP

Clock

GX1 Video Clock

Direct Video Data

TV Clock

Direct VBI Data

F4BAR2

Control

Registers

Video

Mux

VBI

Mux

to Video

Formatter

to TVOUT

Video or VBI Data

GenLock

Control

Stop DCLK

CRT_VSYNC

VIP_VSYNC

VIP