168 AMD Geode™ SC1200/SC1201 Processor Data Book

Core Logic Module

32579B

Physical Region Descriptor Table Address

Before the bus master starts a master transfer it must be pro-

grammed with a pointer (PRD Table Address register) to a

Physical Region Descriptor Table. This pointer sets the start-

ing memory location of the Physical Region Descriptors

(PRDs). The PRDs describe the areas of memory that are

used in the data transfer. The descriptor table entries must be

aligned on a 32-byte boundary and the table cannot cross a

64 KB boundary in memory.

Physical Region Descriptor Format

Each physical memory region to be transferred is

described by a Physical Region Descriptor (PRD) as illus-

trated in Table 6-11. When the bus master is enabled

(Command register bit 0 = 1), data transfer proceeds until

each PRD in the PRD table has been transferred. The bus

master does not cache PRDs.

The PRD table consists of two DWORDs. The first DWORD

contains a 32-bit pointer to a buffer to be transferred. The

second DWORD contains the size (16 bits) of the buffer

and flags (EOT, EOP, JMP). The description of the flags are

as follows:

• EOT bit - If set in a PRD, this bit indicates the last entry

in the PRD table (bit 31). The last entry in a PRD table

must have either the EOT bit or the JMP bit set. A PRD

can not have both the JMP and EOT bits set.

• EOP bit - If set in a PRD and the bus master has

completed the PRD’s transfer, the End of Page bit is set

(Status register bit 0 = 1) and an SMI is generated. If a

second EOP is reached due to the completion of

another PRD before the End of Page bit is cleared, the

Bus Master Error bit is set (Status register bit 1 = 1) and

the bus master pauses. In this paused condition, reading

the Status register clears both the Bus Master Error and

the End of Page bits and the bus master continues.

• JMP bit - This PRD is special. If set, the Memory Region

Physical Base Address is now the target address of the

JMP. The target address must be on a 32-byte boundary

so bits[4:0] must be written to 0. There is no data

transfer with this PRD. This PRD allows the creation of a

looping mechanism. If a PRD table is created with the

JMP bit set in the last PRD, the PRD table does not

need a PRD with the EOT bit set. A PRD can not have

both the JMP and EOT bits set.

Programming Model

The following discussion explains, in steps, how to initiate

and maintain a bus master transfer between memory and

an audio slave device.

In the steps listed below, the reference to “Example” refers

to Figure 6-12 "PRD Table Example" on page 169.

1) Software creates a PRD table in system memory.

Each PRD entry is 8 bytes long; consisting of a base

address pointer and buffer size. The maximum data

that can be transferred from a PRD entry is 64 KB. A

PRD table must be aligned on a 32-byte boundary.

The last PRD in a PRD table must have the EOT or

JMP bit set.

Example - Assume the data is outbound. There are

three PRDs in the example PRD table. The first two

PRDs (PRD_1, PRD_2) have only the EOP bit set.

The last PRD (PRD_3) has only the JMP bit set. This

example creates a PRD loop.

2) Software loads the starting address of the PRD table

by programming the PRD Table Address register.

Example - Program the PRD Table Address register

with Address_3.

3) Software must fill the buffers pointed to by the PRDs

with audio data. It is not absolutely necessary to fill the

buffers; however, the buffer filling process must stay

ahead of the buffer emptying. The simplest way to do

this is by using the EOP flags to generate an SMI

when a PRD is empty.

Example - Fill Audio Buffer_1 and Audio Buffer_2. The

SMI generated by the EOP from the first PRD allows

the software to refill Audio Buffer_1. The second SMI

refills Audio Buffer_2. The third SMI refills Audio

Buffer_1 and so on.

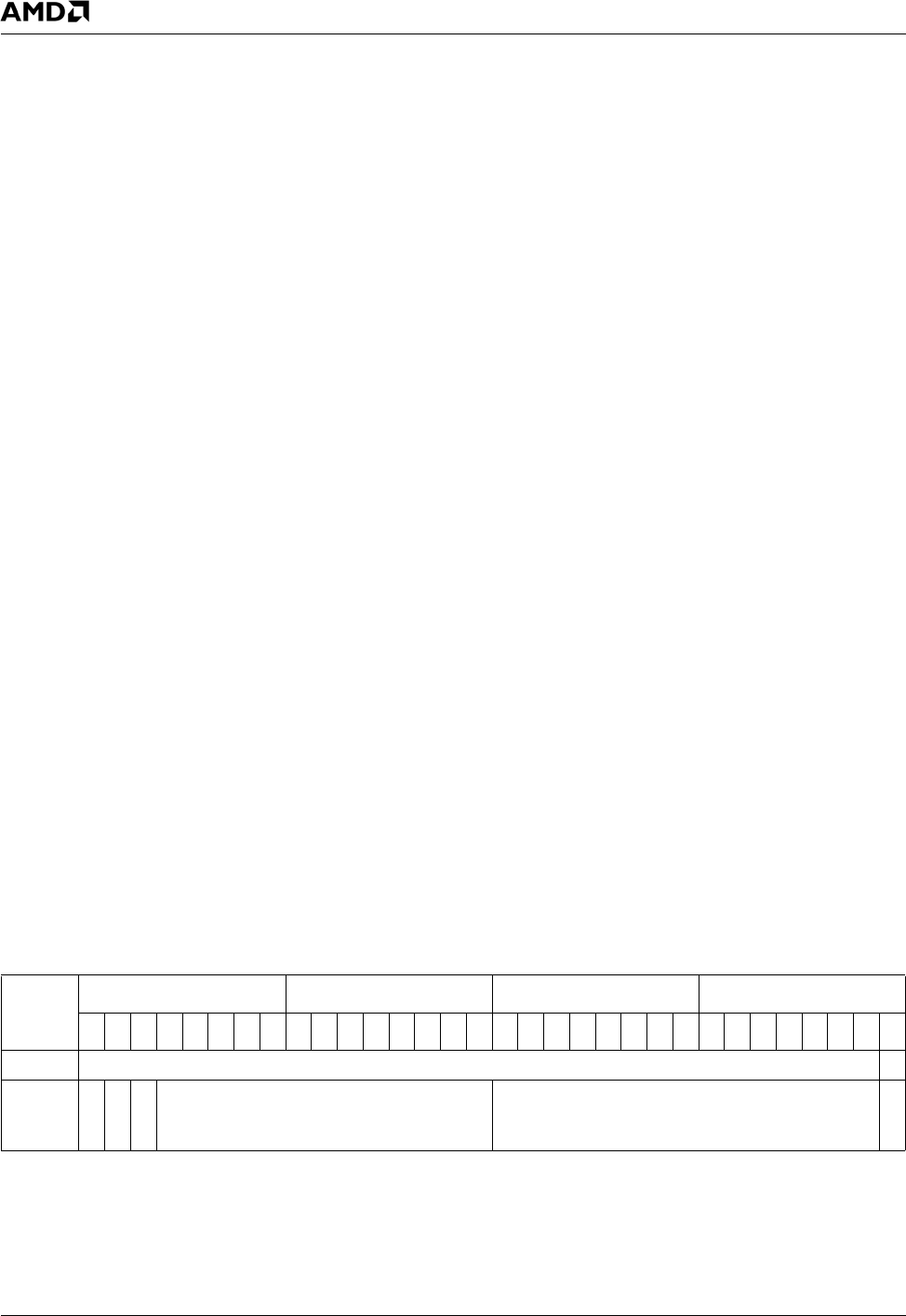

Table 6-11. Physical Region Descriptor Format

DWORD

Byte 3 Byte 2 Byte 1 Byte 0

313029282726252423222120191817161514131211109876543210

0 Memory Region Base Address [31:1] (Audio Data Buffer) 0

1E

O

T

E

O

P

J

M

P

Reserved Size [15:1] 0