AMD Geode™ SC1200/SC1201 Processor Data Book 179

Core Logic Module - Register Summary

32579B

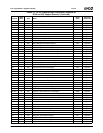

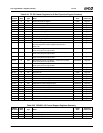

Table 6-15. F0BAR0: GPIO Support Registers Summary

F0BAR0+

I/O Offset

Width

(Bits) Type Name

Reset

Value

Reference

(Table 6-30)

00h-03h 32 R/W GPDO0 — GPIO Data Out 0 Register FFFFFFFFh Page 224

04h-07h 32 RO GPDI0 — GPIO Data In 0 Register FFFFFFFFh Page 224

08h-0Bh 32 R/W GPIEN0 — GPIO Interrupt Enable 0 Register 00000000h Page 224

0Ch-0Fh 32 R/W1C GPST0 — GPIO Status 0 Register 00000000h Page 224

10h-13h 32 R/W GPDO1 — GPIO Data Out 1 Register FFFFFFFFh Page 225

14h-17h 32 RO GPDI1 — GPIO Data In 1 Register FFFFFFFFh Page 225

18h-1Bh 32 R/W GPIEN1 — GPIO Interrupt Enable 1 Register 00000000h Page 225

1Ch-1Fh 32 R/W1C GPST1 — GPIO Status 1 Register 00000000h Page 225

20h-23h 32 R/W GPIO Signal Configuration Select Register 00000000h Page 225

24h-27h 32 R/W GPIO Signal Configuration Access Register 00000044h Page 226

28h-2Bh 32 R/W GPIO Reset Control Register 00000000h Page 227

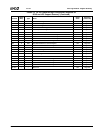

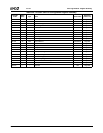

Table 6-16. F0BAR1: LPC Support Registers Summary

F0BAR1+

I/O Offset

Width

(Bits) Type Name

Reset

Value

Reference

(Table 6-31)

00h-03h 32 R/W SERIRQ_SRC — Serial IRQ Source Register 00000000h Page 228

04h-07h 32 R/W SERIRQ_LVL — Serial IRQ Level Control Register 00000000h Page 229

08h-0Bh 32 R/W SERIRQ_CNT — Serial IRQ Control Register 00000000h Page 231

0Ch-0Fh 32 R/W DRQ_SRC — DRQ Source Register 00000000h Page 231

10h-13h 32 R/W LAD_EN — LPC Address Enable Register 00000000h Page 232

14h-17h 32 R/W LAD_D0 — LPC Address Decode 0 Register 00080020h Page 233

18h-1Bh 32 R/W LAD_D1 — LPC Address Decode 1 Register 00000000h Page 234

1Ch-1Fh 32 R/W LPC_ERR_SMI — LPC Error SMI Register 00000080h Page 234

20h-23h 32 RO LPC_ERR_ADD — LPC Error Address Register 00000000h Page 235