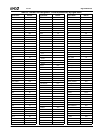

AMD Geode™ SC1200/SC1201 Processor Data Book 47

Signal Definitions

32579B

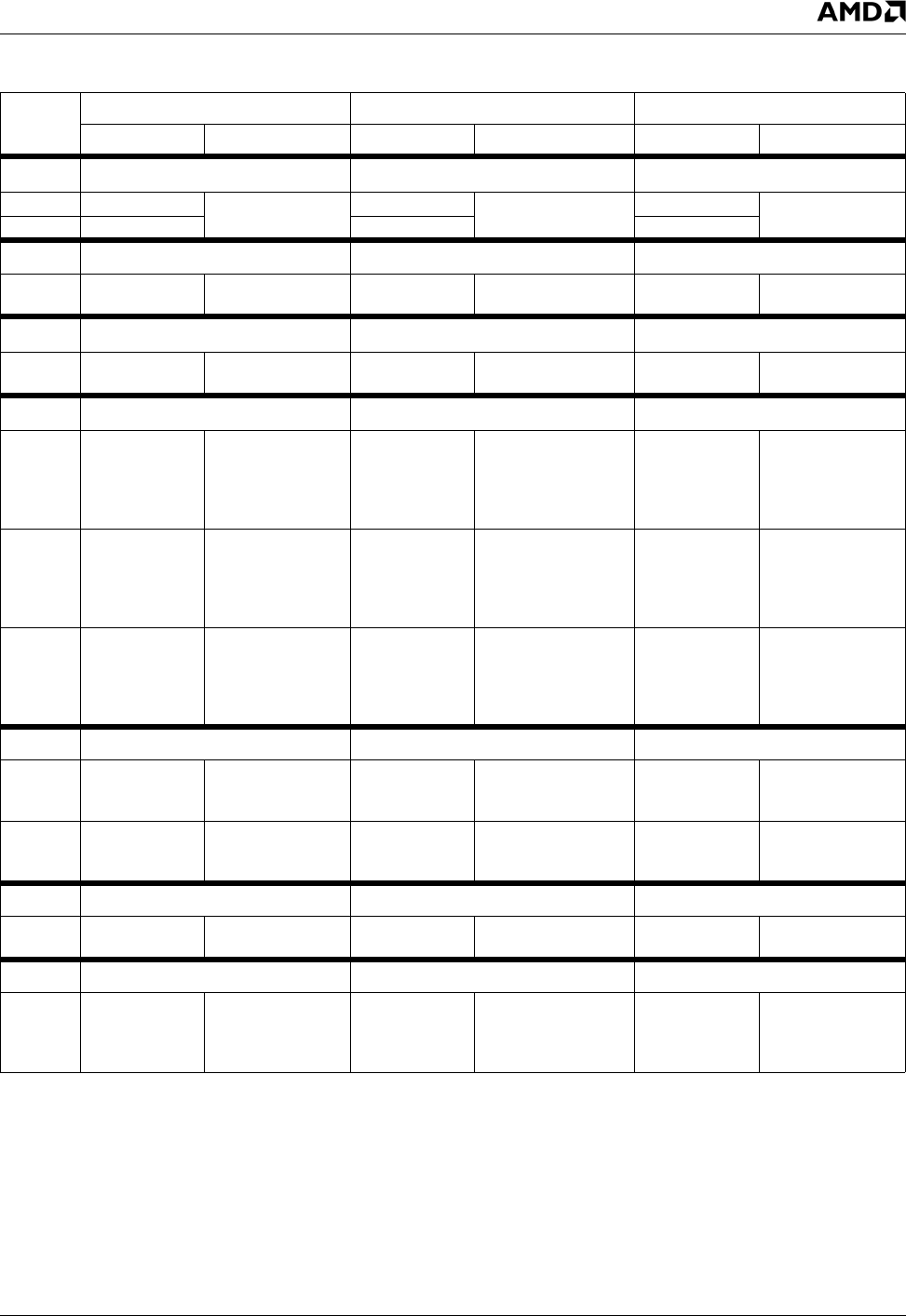

Table 3-6. Three-Signal/Group Multiplexing

Ball No.

Default Alternate1 Alternate2

Signal Configuration Signal Configuration Signal Configuration

Sub-ISA Sub-ISA

1

GPIO

D9 IOR# PMR[21] = 0 and

PMR[2] = 0

DOCR# PMR[21] = 0 and

PMR[2] = 1

GPIO14 PMR[21] = 1 and

PMR[2] = 1

A8 IOW# DOCW# GPIO15

GPIO AC97 FPCI Monitoring

V31 GPIO16 PMR[0] = 0 and

FPCI_MON = 0

PC_BEEP PMR[0] = 1 = 0 and

FPCI_MON = 0

F_DEVSEL FPCI_MON = 1

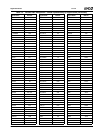

GPIO PCI

2

Sub-ISA

C9 GPIO19 PMR[9] = 0 and

PMR[4] = 0

INTC# PMR[9] = 0 and

PMR[4] = 1

IOCHRDY PMR[9] = 1 and

PMR[4] = 1

GPIO Sub-ISA TFT

3

A10 GPIO17 (PMR[23] = 0 and

PMR[5] = 0) or

(PMR[23] = 1 and

PMR[15] = 1 and

PMR[5] = 0)

IOCS0# (PMR[23] = 0 and

PMR[5] = 1) or

(PMR[23] = 1 and

PMR[15] = 1 and

PMR[5] = 1)

TFTDCK PMR[23] = 1 and

PMR[15] = 0

A9 GPIO20 (PMR[23] = 0 and

PMR[7] = 0) or

(PMR[23] = 1 and

PMR[15] = 1 and

PMR[7] = 0)

DOCCS# (PMR[23] = 0 and

PMR[7] = 1) or

(PMR[23] = 1 and

PMR[15] = 1 and

PMR[7] = 1)

TFTD0 PMR[23] = 1 and

PMR[15] = 0

D10 GPIO1 (PMR[23] = 0 and

PMR[13] = 0) or

(PMR[23] = 1 and

PMR[15] = 1 and

PMR[13] = 0)

IOCS1# (PMR[23] = 0 and

PMR[13] = 1) or

(PMR[23] = 1 and

PMR[15] = 1 and

PMR[13] = 1)

TFTD12 PMR[23] = 1 and

PMR[15] = 0

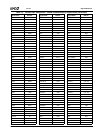

AB1 GPIO Sub-ISA

N31 AB1C PMR[23] = 0 or

(PMR[23] = 1 and

PMR[15] = 1)

GPIO20 PMR[23] = 1 and

PMR[15] = 0 and

PMR[7] = 0

DOCCS# PMR[23] = 1 and

PMR[15] = 0 and

PMR[7] = 1

N30 AB1D PMR[23] = 0 or

(PMR[23] = 1 and

PMR[15] = 1)

GPIO1 PMR[23] = 1 and

PMR[15] = 0 and

PMR[13] = 0

IOCS1# PMR[23] = 1 and

PMR[15] = 0 and

PMR[13] = 1

GPIO UART2 IDE2

AJ8 GPIO11 PMR[18] = 0 and

PMR[8] = 0

RI2# PMR[18] = 1 and

PMR[8] = 0

IRQ15 PMR[18] = 0 and

PMR[8] = 1

Internal Test TFT Internal Test

V30 GXCLK (PMR[29] = 0 and

PMR[23] = 0) or

(PMR[23] = 1 and

PMR[15] = 1)

FP_VDD_ON PMR[23] = 1 and

PMR[15] = 0

TEST3 PMR[29] = 1 and

PMR[23] = 0

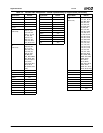

1. The combination of PMR[21] = 1 and PMR[2] = 0 is undefined and should not be used.

2. The combination of PMR[9] = 1 and PMR[4] = 0 is undefined and should not be used.

3. These TFT outputs are reset to 0 by POR# if the TFT_PRSNT strap is pulled high or PMR[10] = 0. This relates to signals TFTD[17:0],

TFTDE, TFTDCK.