286 AMD Geode™ SC1200/SC1201 Processor Data Book

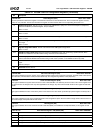

Core Logic Module - USB Controller Registers - PCIUSB

32579B

7:6 HostControllerFunctionalState. This field sets the HC state. The HC may force a state change from UsbSuspend to

UsbResume after detecting resume signaling from a downstream port. States are:

00: UsbReset

01: UsbResume

10: UsbOperational

11: UsbSuspend

5 BulkListEnable. When set, this bit enables processing of the Bulk list.

4 ControlListEnable. When set, this bit enables processing of the Control list.

3 IsochronousEnable. When clear, this bit disables the Isochronous List when the Periodic List is enabled (so Interrupt EDs

may be serviced). While processing the Periodic List, the HC will check this bit when it finds an isochronous ED.

2 PeriodicListEnable. When set, this bit enables processing of the Periodic (interrupt and isochronous) list. The HC checks

this bit prior to attempting any periodic transfers in a frame.

1:0 ControlBulkServiceRatio. Specifies the number of Control Endpoints serviced for every Bulk Endpoint. Encoding is N-1

where N is the number of Control Endpoints (i.e., 00: 1 Control Endpoint; 11: 3 Control Endpoints).

Offset 08h-0Bh HcCommandStatus Register (R/W) Reset Value = 00000000h

31:18 Reserved. Read/Write 0s.

17:16 ScheduleOverrunCount. This field increments every time the SchedulingOverrun bit in HcInterruptStatus is set. The

count wraps from 11 to 00.

15:4 Reserved. Read/Write 0s.

3 OwnershipChangeRequest. When set by software, this bit sets the OwnershipChange field in HcInterruptStatus. The bit

is cleared by software.

2 BulkListFilled. Set to indicate there is an active ED on the Bulk List. The bit may be set by either software or the HC and

cleared by the HC each time it begins processing the head of the Bulk List.

1 ControlListFilled. Set to indicate there is an active ED on the Control List. It may be set by either software or the HC and

cleared by the HC each time it begins processing the head of the Control List.

0 HostControllerReset. This bit is set to initiate a software reset. This bit is cleared by the HC upon completion of the reset

operation.

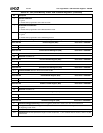

Offset 0Ch-0Fh HcInterruptStatus Register (R/W) Reset Value = 00000000h

31 Reserved. Read/Write 0s.

30 OwnershipChange. This bit is set when the OwnershipChangeRequest bit of HcCommandStatus is set.

29:7 Reserved. Read/Write 0s.

6 RootHubStatusChange. This bit is set when the content of HcRhStatus or the content of any HcRhPortStatus register has

changed.

5 FrameNumberOverflow. Set when bit 15 of FrameNumber changes value.

4 UnrecoverableError (Read Only). This event is not implemented and is hard-coded to 0. Writes are ignored.

3 ResumeDetected. Set when HC detects resume signaling on a downstream port.

2 StartOfFrame. Set when the Frame Management block signals a Start of Frame event.

1 WritebackDoneHead. Set after the HC has written HcDoneHead to HccaDoneHead.

0 SchedulingOverrun. Set when the List Processor determines a Schedule Overrun has occurred.

Note: All bits are set by hardware and cleared by software.

Table 6-42. USB_BAR+Memory Offset: USB Controller Registers (Continued)

Bit Description