352 AMD Geode™ SC1200/SC1201 Processor Data Book

Video Processor Module - Video Processor Registers - Function 4

32579B

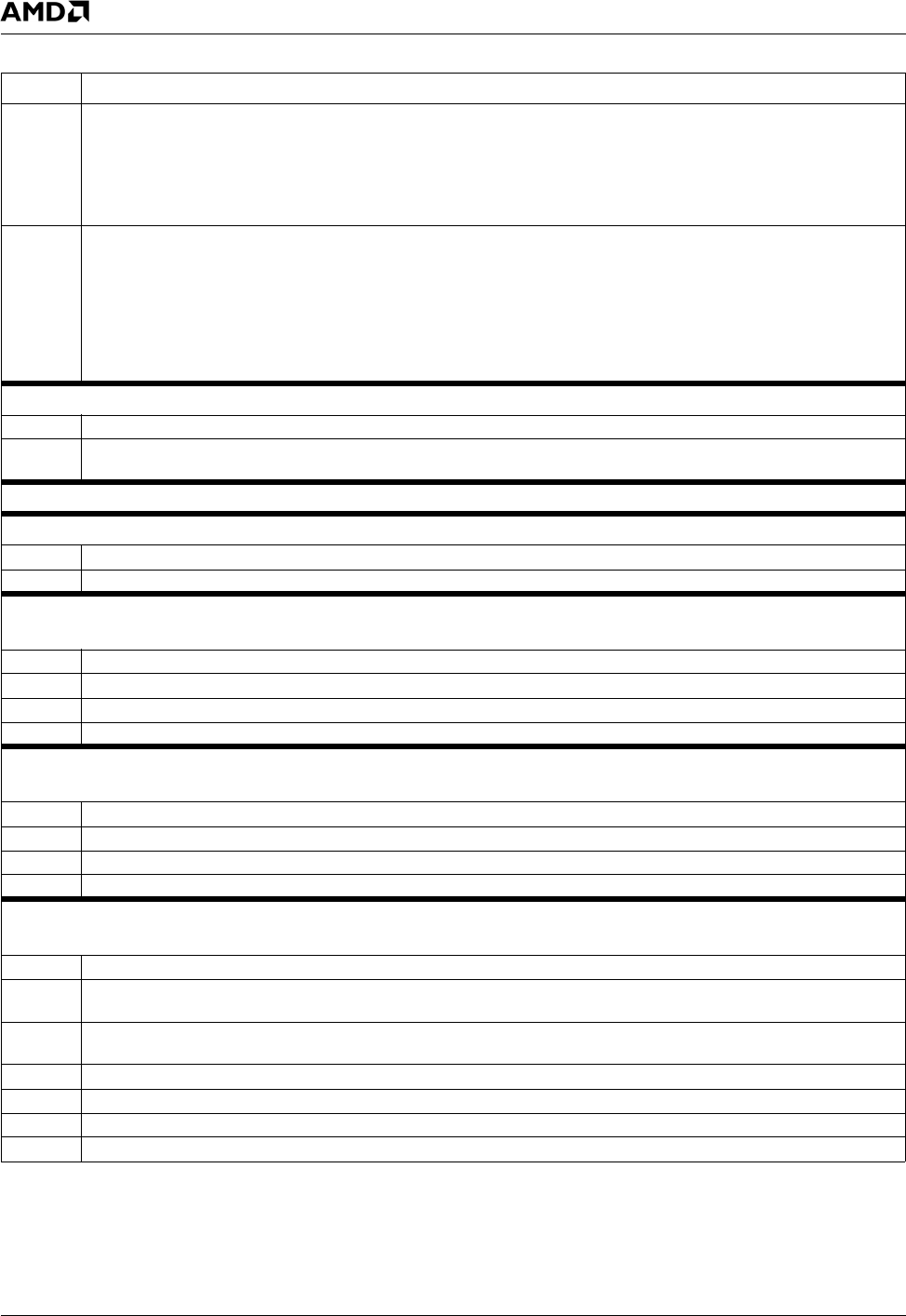

1 CT_GENLOCK_EN (Enable Continuous GenLock Function).

0: The continuous GenLock function is disabled.

1: Enable locking (i.e., synchronization) of the GX1 VSYNC with the VIP VSYNC on every VSYNC (i.e., continuous lock-

ing).

Note: If bit 0 (SG_GENLOCK_EN) = 1, it overrides the value of this bit.

0 SG_GENLOCK_EN (Enable a Single GenLock Function).

0: GenLock is disabled if bit 1 (CT_GENLOCK_EN) = 0.

1: Enable synchronization (i.e., locking) of GX1 VSYNC with the VIP VSYNC and synchronization of the TV encoder field

with the VIP field, once. During the synchronization process, the TV encoder field is determined by bit 5 of this register.

When in Direct Video mode, it is critical that the field of the TV encoder and the Video Input Port (F4BAR2+Memory Off-

set 08h[24]) be the same after the synchronization event. After locking once, this bit is reset by hardware to 0.

Note: If this bit = 1, it overrides the value of bit 1 (CT_GENLOCK_EN).

Offset 424h-427h GenLock Delay Register (R/W) Reset Value: 00000000h

31:21 Reserved.

20:0 GENLOCK_DEL (GenLock Delay). Indicates the delay (in 27 MHz clocks) between the VIP VSYNC and the GX1 module’s

Display Controller VSYNC.

Offset 428h-43Bh Reserved

Offset 43Ch-43Fh Continuous GenLock Timeout Register (R/W) Reset Value: 1FFF1FFFh

31:16 CGENTO1 (Even Field Continuous GenLock Timeout).

15:0 CGENTO0 (Odd Field Continuous GenLock Timeout).

Offset 800h-803h Horizontal Timing Register (R/W) Reset Value: 00000000h

This register is updated at each occurrence of HSYNC.

31:28 Reserved.

27:16 H_DISP_START (Horizontal Display Start). Specifies the first horizontal valid pixel position on a TV screen, in pixel clocks.

15:12 Reserved.

11:0 H_TOTAL (Horizontal Total). Specifies the total number of pixels per line - 1, for TV. For NTSC, use 857; for PAL use 863.

Offset 804h-807h Horizontal Sync Timing Register (R/W) Reset Value: 00000000h

This register is updated at each occurrence of HSYNC.

31:28 Reserved.

27:16 H_SYNC_END (Horizontal Sync End). Specifies the horizontal synchronization end position in pixel clocks.

15:12 Reserved.

11:0 H_SYNC_START (Horizontal Sync Start). Specifies the horizontal synchronization start position in pixel clocks.

Offset 808h-80Bh Vertical Sync Timing Register (R/W) Reset Value: 00000000h

This register is updated at each occurrence of VSYNC.

31:28 Reserved.

27:26 V_DISP_SKEW_EVEN (Vertical Display Skew). Specifies the vertical display end skew in terms of horizontal lines for all

even fields. Recommended value is 1.

25:24 V_DISP_SKEW_ODD (Vertical Display Skew). Specifies the vertical display start skew in terms of horizontal lines for all

odd fields. Recommended value is 1.

23:22 Reserved.

21:12 V_SYNC_END (Vertical Sync End). Specifies the vertical synchronization end position in terms of horizontal lines.

11:10 Reserved.

9:0 VSYNC_START (Vertical Sync Start). Specifies the vertical synchronization start position in terms of horizontal lines.

Table 7-9. F4BAR0+Memory Offset: Video Processor Configuration Registers (Continued)

Bit Description