Hardware Description

ARM DUI 0125A

© Copyright ARM Limited 1999. All rights reserved.

3-17

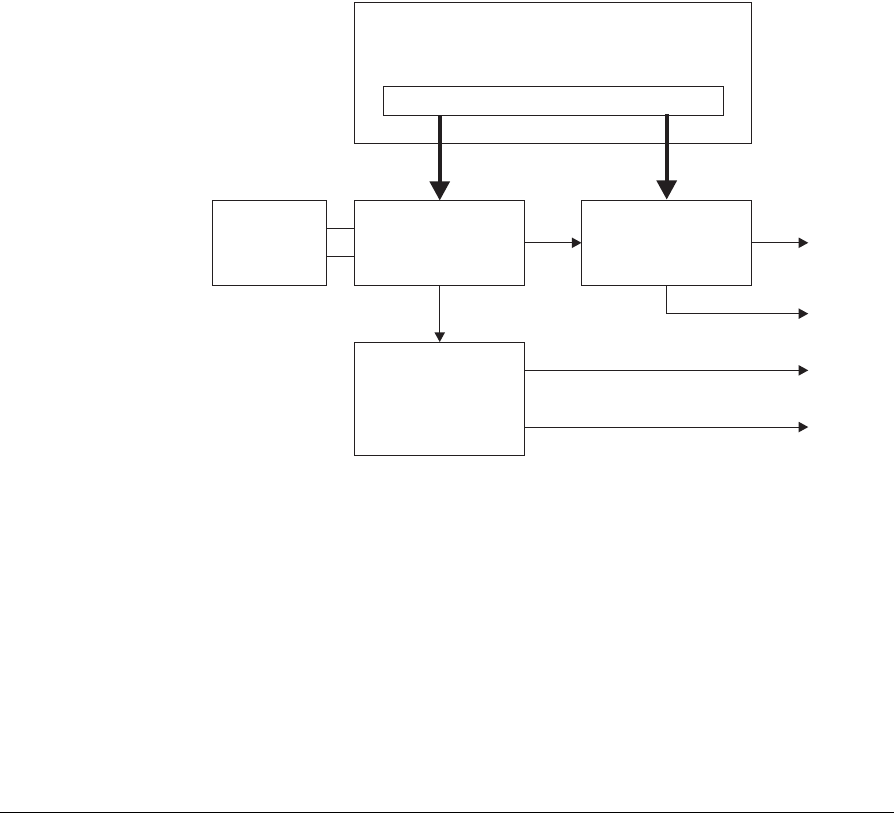

3.7 Clock generators

The core module provides its own clock generators and operates asynchronously with

the motherboard. The clock generator provides two programmable clocks:

• processor core clock CORECLK

• processor local memory bus clocks LCLK and nLCLK.

In addition, a fixed-frequency reference clock REFCLK is supplied to the FPGA.

These clocks are supplied by two MicroClock ICS525 devices and by the SSRAM

controller PLD, as illustrated in Figure 3-9.

Figure 3-9 Core module clock generator

The ICS525s are supplied with a reference clock signal from a 24MHz crystal

oscillator. The 2XCLK output from the first ICS525 (U6) is supplied to the PLD and

divided by two to produce the signals LCLK and nLCLK. The output from U7

provides the CORECLK signal. The reference output from U6 supplies the reference

input to U7 and the reference output from U7 supplies the FPGA reference clock.

The output frequencies from the ICS525s are configured using divider input pins to

produce a wide range of frequencies.

24MHz

crystal

ICS525

(U6)

ICS525

(U7)

SSRAM controller

(PLD)

FPGA

CM_OSC register

CORECLK

REFCLK

LCLK

nLCLK

2XCLK