Programmer’s Reference

4-20

© Copyright ARM Limited 1999. All rights reserved.

ARM DUI 0125A

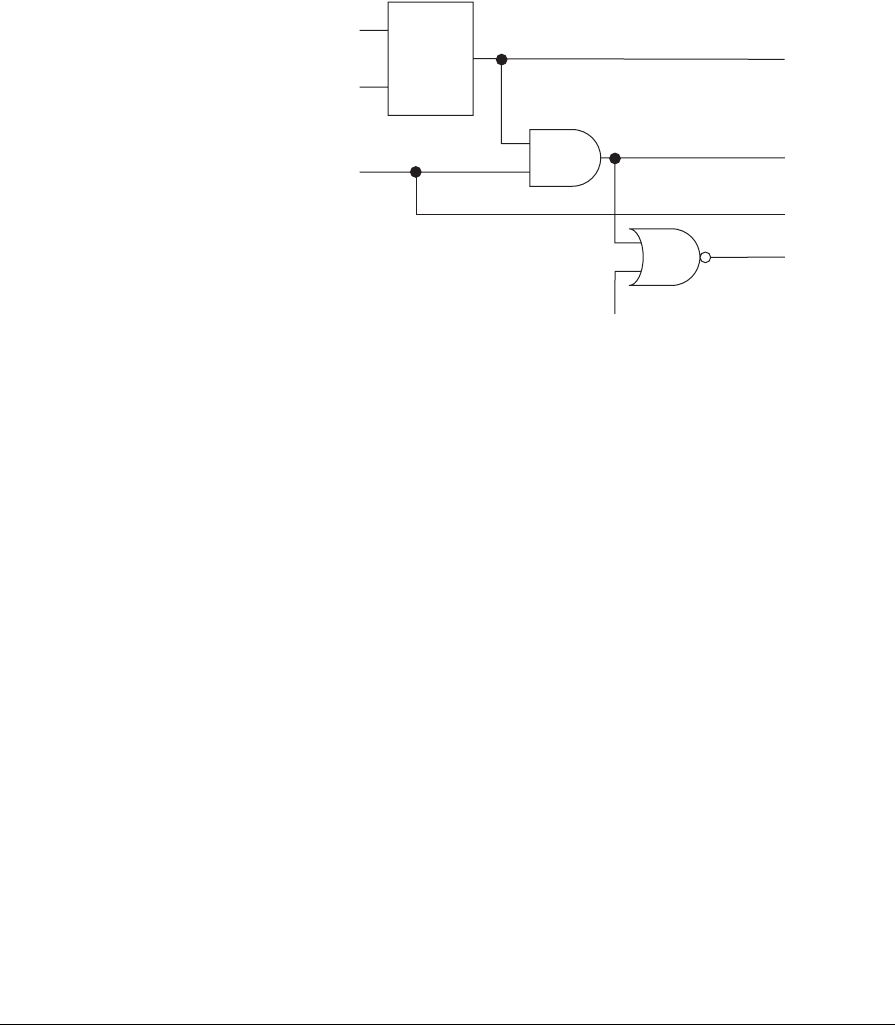

Figure 4-4 Interrupt control

4.4.1 CM_IRQ_STAT (0x10000040)/CM_FIQ_STAT (0x10000060)

The status register contains the logical AND of the bits in the raw status register and the

enable register.

4.4.2 CM_IRQ_RSTAT (0x10000044)/CM_FIQ_RSTAT (0x10000064)

The raw status register indicates the signal levels on the interrupt request inputs. A bit

set to 1 indicates that the corresponding interrupt request is active.

4.4.3 CM_IRQ_ENSET (0x10000048)/CM_FIQ_ENSET (0x10000068)

The enable set locations are used to set bits in the enable register as follows:

• set bits in the enable register by writing to the ENSET location for the required

IRQ or FIQ controller:

1 = SET the bit.

0 = leave the bit unchanged.

• read the current state of the enable bits from the ENSET location.

Set

Clear

Enable

Status

Raw status

Enable set

Interrupt source

Enable clear

From other

bit slices

nIRQ