Programmer’s Reference

ARM DUI 0125A

© Copyright ARM Limited 1999. All rights reserved.

4-9

4.3.3 CM_OSC (0x10000008)

The core module oscillator register (CM_OSC) is a read/write register that controls the

frequency of the clocks generated by the two clock generators (see Clock generators on

page 3-17). In addition, it provides information about processor bus mode setting.

Before writing to the CM_OSC register, you must unlock it by writing the value

0x0000A05F to the CM_LOCK register. After writing the CM_OSC register, relock it

by writing any value other than 0x0000A05F to the CM_LOCK register.

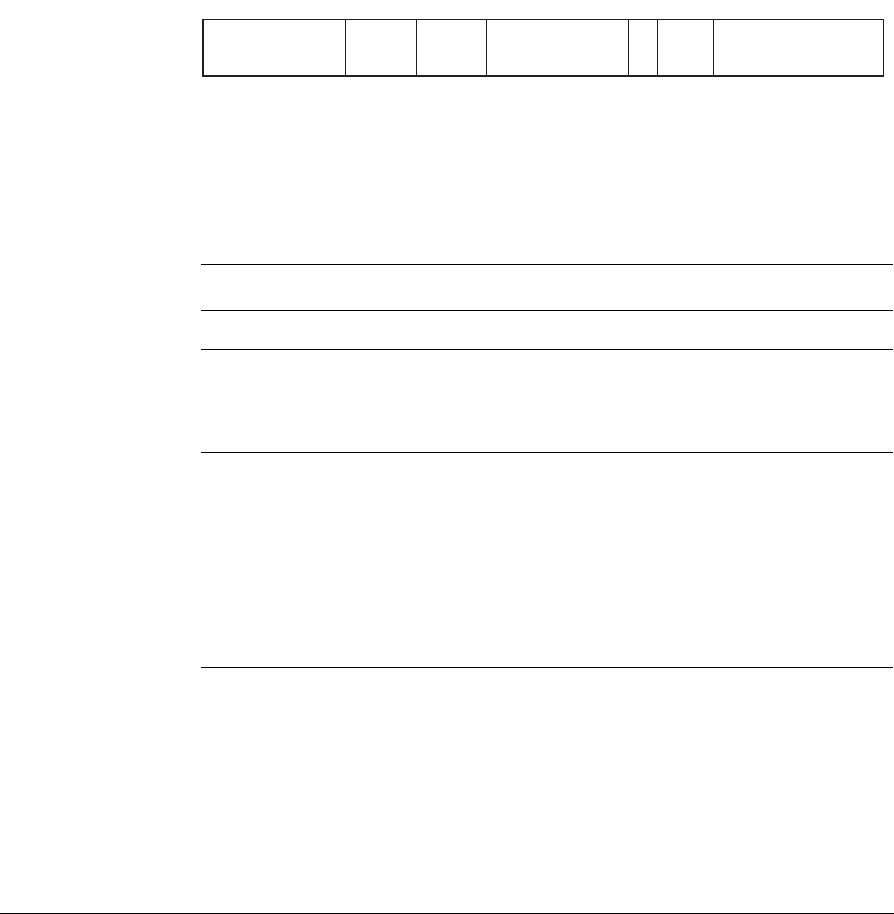

Table 4-4 describes the core module oscillator register bits.

Table 4-4 CM_OSC register

Bits Name Access Function

31:25 Reserved Use read-modify-write to preserve value.

24:23 BMOD Read This field contains 00 which indicates that the

processor bus mode is selected by writing to

CM_CTRL register (see CM_CTRL

(0x1000000C) on page 4-11).

22:20 L_OD Read/write Memory clock output divider:

000 = divide by 10

001 = divide by 2 (default)

010 = divide by 8

011 = divide by 4

100 = divide by 5

101 = divide by 7

110 = divide by 9

111 = divide by 6.

19:12 L_VDW Read/write Processor bus clock VCO divider word.

Defines the binary value of the V[7:0] pins of

the clock generator (V[8] is tied low).

00000100 = 6MHz (default with OD = 2).

31

25

24

23 22 20

19

12 11 10 780

Reserved

L_ODBMODE

L_VDW

C_OD

C_VDWR