Hardware Description

3-18

© Copyright ARM Limited 1999. All rights reserved.

ARM DUI 0125A

3.7.1 Processor core clock (CORECLK)

The frequency of CORECLK is controllable in 1MHz steps in the range 12MHz to

160MHz. This is achieved by setting the Voltage Controlled Oscillator (VCO) divider

and output divider for the CORECLK generator via the CM_OSC register. The VCO

divider is controlled by the C_VDW bits and output divider is controlled by the C_OD

bits. The reference divider value is fixed.

Table 3-2 shows the values placed on the divider input pins and how the clock speeds

are derived. The bits marked:

• C are programmable in the CM_OSC register

• 1 are tied HIGH

• 0 are tied LOW.

The frequency of CORECLK can be derived from the formula:

freq = 2*((C_VDW+ 8)/C_OD)

where:

C_VDW is the VCO divider word for the core clock.

C_OD is the output divider for the core clock.

For details about programming C_VDW and C_OD, see CM_OSC (0x10000008) on

page 4-9.

Note

Values for C_VDW and C_OD can be calculated using the ICS525 calculator on the

Microclock website.

The CORECLK is buffered with a PI49FCT3805 to convert the Phase-Locked Loop

(PLL) output to 3.3V signal level. The clock is series terminated with a 33Ω resistor and

then drives a single load on the microprocessor core.

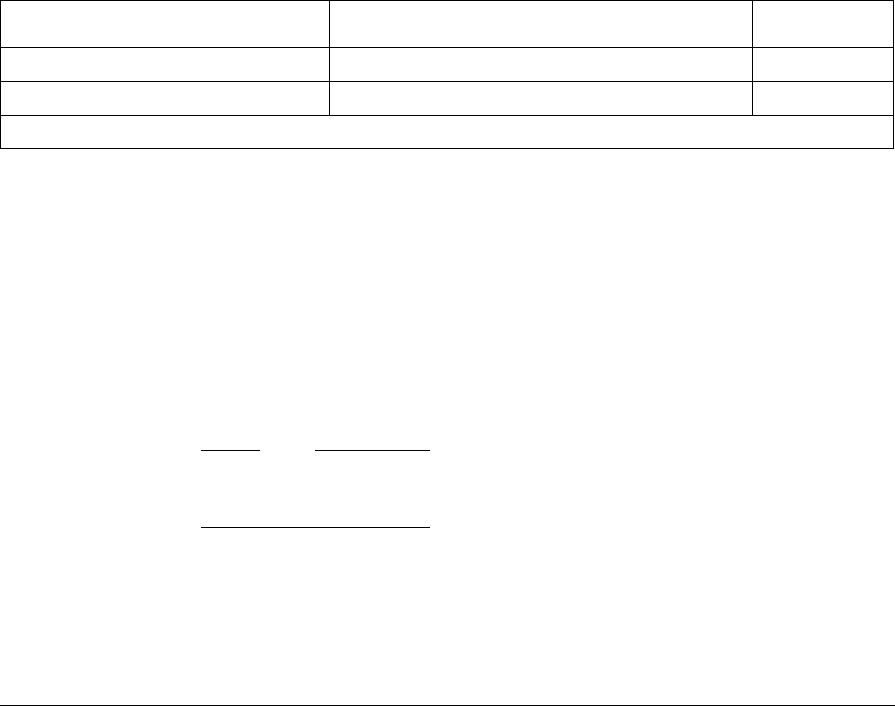

Table 3-2 CORECLK divider values

C_RDW R[6:0] C_VDW V[8:0] C_OD S[2:0]

00101100CCCCCCCCCCC

22 (fixed value) 4 – 152 (<4 and >152 not allowed) 2-10

12 – 160MHz in 1MHz steps