Hardware Description

ARM DUI 0125A

© Copyright ARM Limited 1999. All rights reserved.

3-25

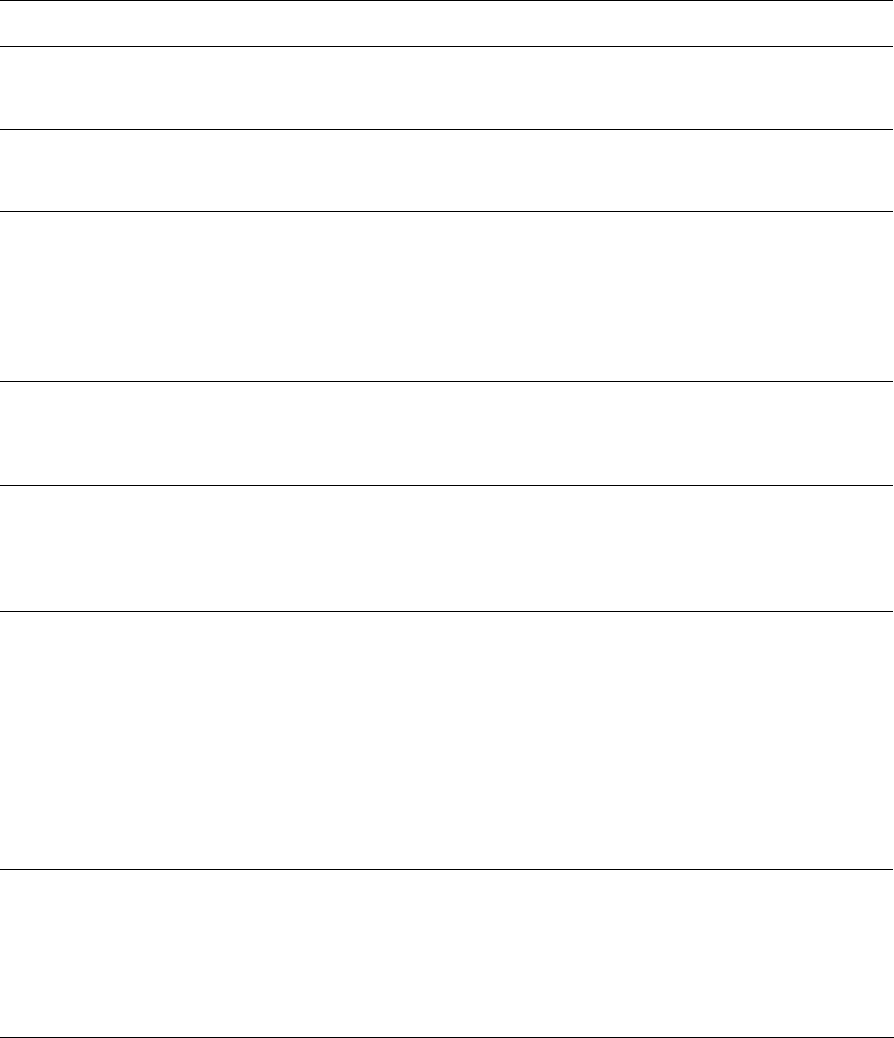

Table 3-4 JTAG signal description

Name Description Function

DBGRQ Debug request

(from JTAG equipment)

DBGRQ is a request for the processor core to enter the debug

state. It is provided for compatibility with third-party JTAG

equipment.

DBGACK Debug acknowledge

(to JTAG equipment)

DBGACK indicates to the debugger that the processor core has

entered debug mode. It is provided for compatibility with

third-party JTAG equipment.

DONE FPGA configured DONE is an open-collector signal which indicates when FPGA

configuration is complete. Although this signal is not a JTAG

signal, it does effect nSRST. The DONE signal is routed between

all FPGAs in the system through the HDRB connectors. The

master reset controller on the motherboard senses this signal and

holds all the boards in reset (by driving nSRST LOW) until all

FPGAs are configured.

nCFGEN Configuration enable

(from jumper on module at the

top of the stack)

nCFGEN is an active LOW signal used to put the boards into

configuration mode. In configuration mode all FPGAs and PLDs

are connected to the scan chain so that they can be configured by

the JTAG equipment.

nRTCKEN Return TCK enable (from core

module to motherboard)

nRTCKEN is an active LOW signal driven by any core module

that requires RTCK to be routed back to the JTAG equipment. If

nRTCKEN is HIGH, the motherboard drives RTCK LOW. If

nRTCKEN is LOW, the motherboard drives the TCK signal

back up the stack to the JTAG equipment.

nSRST System reset (bidirectional) nSRST is an active LOW open-collector signal which can be

driven by the JTAG equipment to reset the target board. Some

JTAG equipment senses this line to determine when a board has

been reset by the user.

The open collector nRST reset signal may be driven LOW by the

reset controller on the core module to cause the motherboard to

reset the whole system by driving nSYSRST LOW.

This is also used in configuration mode to control the

initialization pin (nINIT) on the FPGAs.

Though not a JTAG signal, nSRST is described because it can be

controlled by JTAG equipment.

nTRST Test reset (from JTAG

equipment)

This active low open-collector is used to reset the JTAG port and

the associated debug circuitry on the ARM940T processor. It is

asserted at power-up by each module, and can be driven by the

JTAG equipment. This signal is also used in configuration mode

to control the programming pin (nPROG) on FPGAs.