Programmer’s Reference

4-14

© Copyright ARM Limited 1999. All rights reserved.

ARM DUI 0125A

4.3.7 CM_SDRAM (0x10000020)

The SDRAM status and control register (CM_SDRAM) is a read/write register used to

set the configuration parameters for the SDRAM DIMM. This control is necessary

because of the variety of module sizes and types available.

Writing a value to this register automatically updates the mode register on the SDRAM

DIMM.

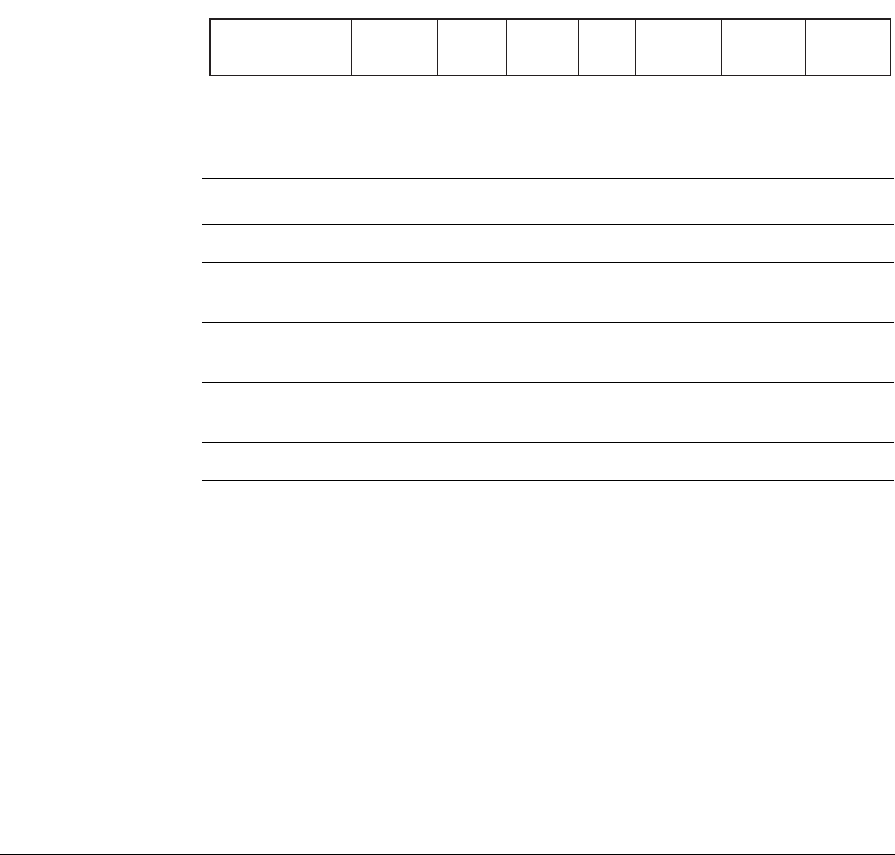

Table 4-8 describes the SDRAM status and control register bits.

Table 4-8 CM_SDRAM register

Bits Name Access Function

31:20 Reserved Use read-modify-write to preserve value.

19:16 NBANKS Read/write Number of SDRAM banks. Should be set to

the same value as byte 5 of SPD EEPROM.

15:12 NCOLS Read/write Number of SDRAM columns. Should be set

to the same value as byte 4 of SPD EEPROM.

11:8 NROWS Read/write Number of SDRAM rows. Should be set to

the same value as byte 3 of SPD EEPROM.

7:6 Reserved Use read-modify-write to preserve value.

5

SPDOK

Read This bit indicates that the automatic copying

of the SPD data from the SDRAM module

into CM_SPDMEM is complete:

1 = SPD data ready

0 = SPD data not available.

31 076 5 4 2111 81216 151920

Reserved

CASLATMEMSIZESPDOKRNROWSNCOLSNBANKS