System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-29

ID013010 Non-Confidential, Unrestricted Access

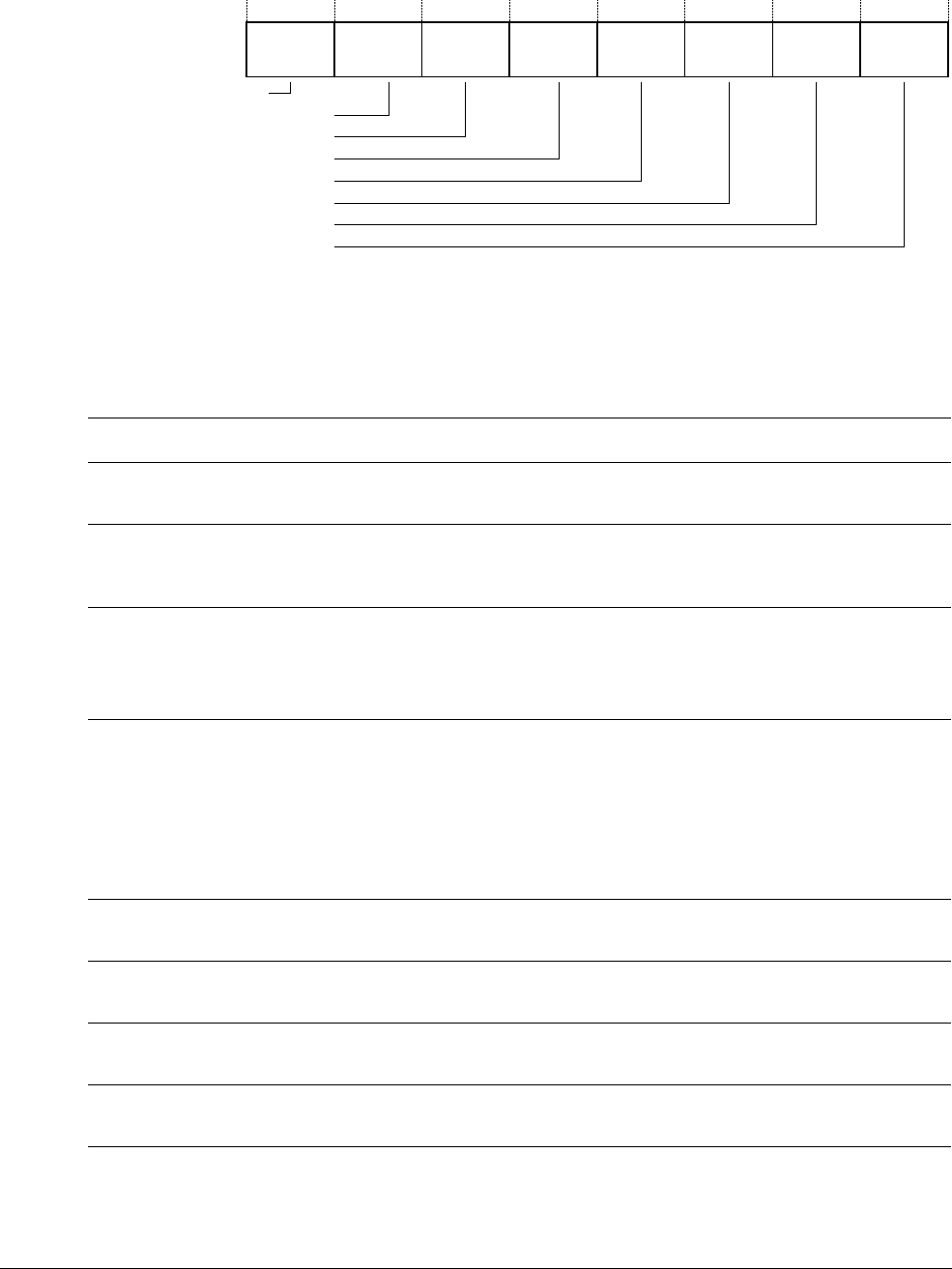

Figure 4-21 shows the bit arrangement for Instruction Set Attributes Register 2.

Figure 4-21 Instruction Set Attributes Register 2 format

Table 4-16 shows how the bit values correspond with the Instruction Set Attributes Register 2

functions.

To access the Instruction Set Attributes Register 2 read CP15 with:

MRC p15, 0, <Rd>, c0, c2, 2 ; Read Instruction Set Attributes Register 2

31 28 27 24 23 20 19 16 15 12 11 8 7 4 3 0

Reversal instructions

PSR instructions

Unsigned multiply instructions

Signed multiply instructions

Multiply instructions

Interruptible instructions

Memory hint instructions

Load/store instructions

Table 4-16 Instruction Set Attributes Register 2 bit functions

Bits Field Function

[31:28] Reversal

instructions

Indicates support for reversal instructions.

0x2

, the processor supports

REV

,

REV16

,

REVSH

, and

RBIT

.

[27:24] PSR

instructions

Indicates support for

PSR

instructions.

0x1

, the processor supports

MRS

and

MSR

, and the exception return forms of data-processing

instructions.

[23:20] Unsigned

multiply

instructions

Indicates support for advanced unsigned multiply instructions.

0x2

, the processor supports:

•

UMULL

and

UMLAL

•

UMAAL

.

[19:16] Signed

multiply

instructions

Indicates support for advanced signed multiply instructions.

0x3

, the processor supports:

•

SMULL

and

SMLAL

•

SMLABB

,

SMLABT

,

SMLALBB

,

SMLALBT

,

SMLALTB

,

SMLALTT

,

SMLATB

,

SMLATT

,

SMLAWB

,

SMLAWT

,

SMULBB

,

SMULBT

,

SMULTB

,

SMULTT

,

SMULWB

,

SMULWT

, and Q flag in PSRs

•

SMLAD

,

SMLADX

,

SMLALD

,

SMLALDX

,

SMLSD

,

SMLSDX

,

SMLSLD

,

SMLSLDX

,

SMMLA

,

SMMLAR

,

SMMLS

,

SMMLSR

,

SMPUL

,

SMPULR

,

SMUAD

,

SMUADX

,

SMUSD

, and

SMUSDX

.

[15:12] Multiply

instructions

Indicates support for multiply instructions.

0x2

, the processor supports

MUL

,

MLA

, and

MLS

.

[11:8] Interruptible

instructions

Indicates support for multi-access interruptible instructions.

0x1

, the processor supports restartable

LDM

and

STM

.

[7:4] Memory hint

instructions

Indicates support for memory hint instructions.

0x3

, the processor supports

PLD

and

PLI

.

[3:0] Load/store

instructions

Indicates support for additional load and store instructions.

0x1

, the processor supports

LDRD

and

STRD

.