AC Characteristics

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 15-5

ID013010 Non-Confidential, Unrestricted Access

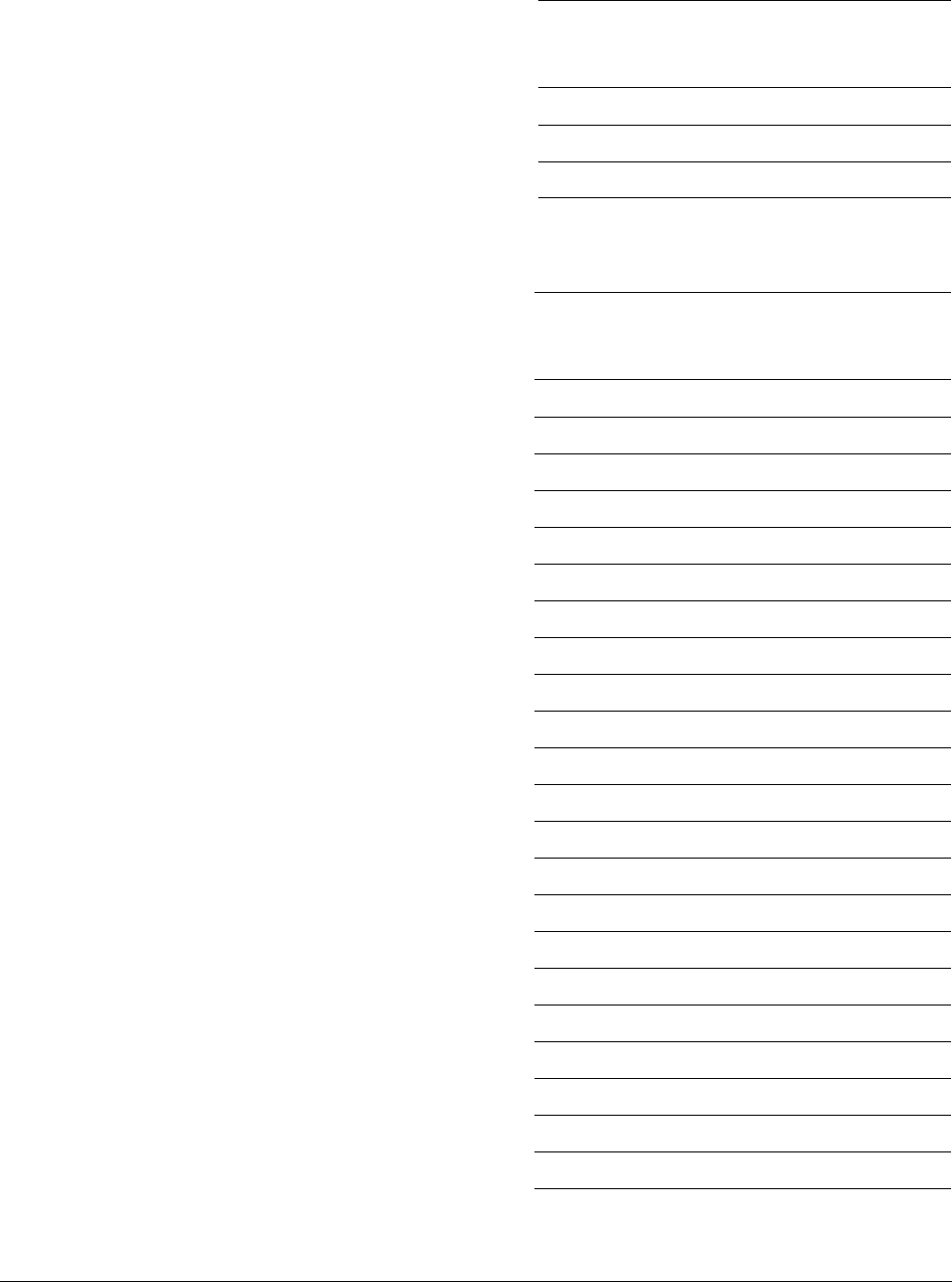

Table 15-5 shows the input timing parameters for the AXI slave port.

Clock uncertainty 60% RVALIDM

Clock uncertainty 60% BPARITYM

Clock uncertainty 60% RPARITYM

Table 15-5 AXI slave input port timing parameters

Input delay

minimum

Input

delay

maximum

Signal name

Clock uncertainty 50% ACLKENS

Clock uncertainty 60% AWIDS [7:0 ]

Clock uncertainty 60% AWADDRS[22:0]

Clock uncertainty 60% AWLENS[3:0]

Clock uncertainty 60% AWSIZES[2:0]

Clock uncertainty 60% AWBURSTS[1:0]

Clock uncertainty 60% AWPRO TS

Clock uncertainty 60% AWUSE RS[ 3:0]

Clock uncertainty 60% AWVA LIDS

Clock uncertainty 60% WDATAS[63:0]

Clock uncertainty 60% WSTRBS[7:0]

Clock uncertainty 60% WLASTS

Clock uncertainty 60% WVALIDS

Clock uncertainty 60% BREADYS

Clock uncertainty 60% ARIDS[7:0]

Clock uncertainty 60% ARADDRS[22:0]

Clock uncertainty 60% ARLENS[3:0]

Clock uncertainty 60% ARSIZES[2:0]

Clock uncertainty 60% ARBURSTS[1:0]

Clock uncertainty 60% ARPROTS

Clock uncertainty 60% ARUSERS[3:0]

Clock uncertainty 60% ARVALIDS

Clock uncertainty 60% RREADYS

Table 15-4 AXI master input port timing parameters (continued)

Input delay

minimum

Input

delay

maximum

Signal name