FPU Programmer’s Model

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 12-7

ID013010 Non-Confidential, Unrestricted Access

12.3.3 Floating-Point Exception Register, FPEXC

The FPEXC Register is a read/write register accessible in Privileged modes only.

The EN bit, FPEXC[30], is the VFP enable bit. Clearing EN disables VFP functionality, causing

all VFP instructions apart from privileged system register accesses to generate an UNDEFINED

exception. The EN bit is cleared on reset.

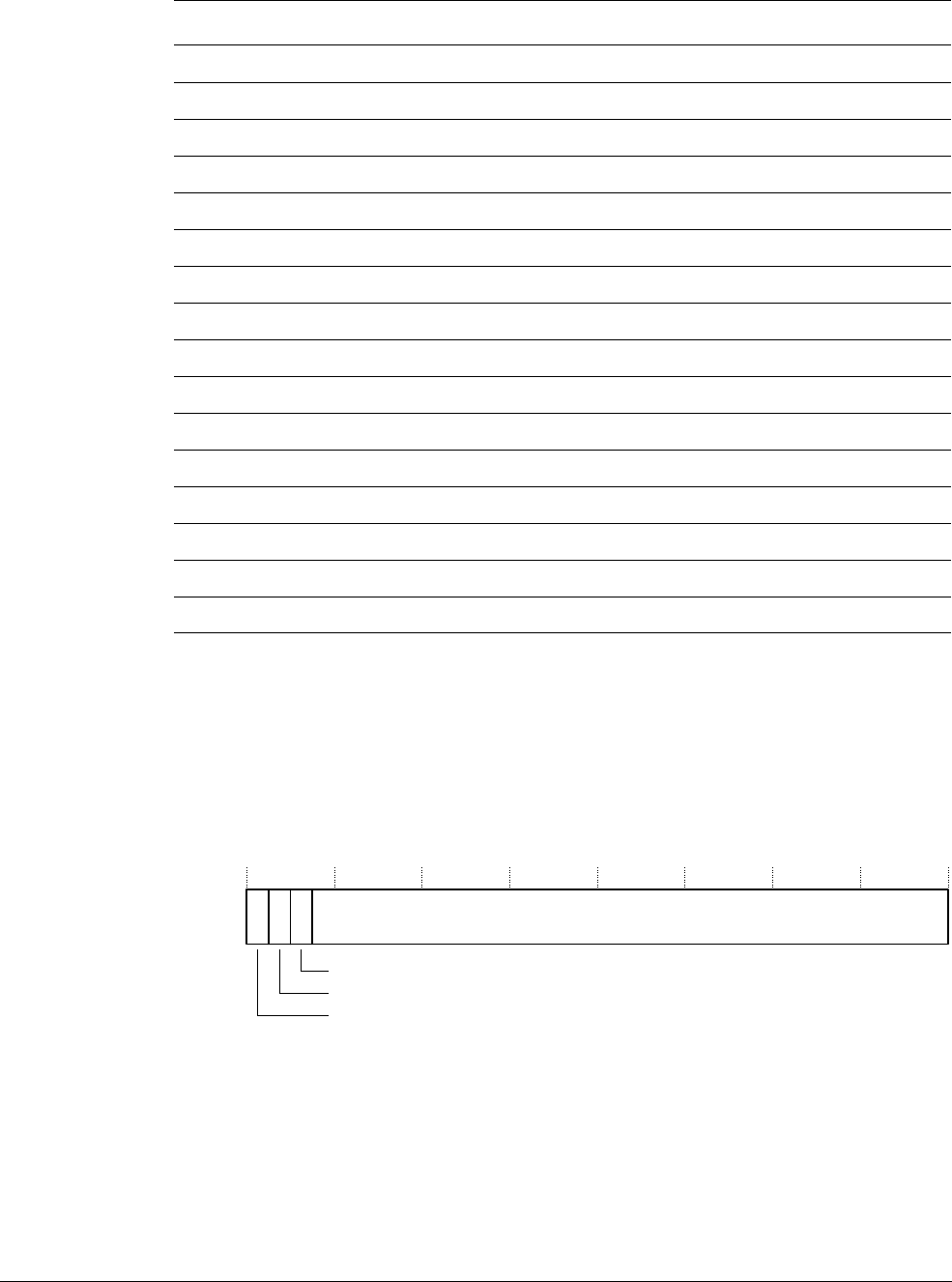

Figure 12-4 shows the bit arrangement of the FPEXC Register.

Figure 12-4 Floating-Point Exception Register format

[19] DNM DNM

[18:16] LEN Indicates the vector length, reset value is

0x0

[15] IDE RAZ

[14:13] DNM DNM

[12] IXE RAZ

[11] UFE RAZ

[10] OFE RAZ

[9] DZE RAZ

[8] IOE RAZ

[7] IDC Input Subnormal cumulative flag, resets to zero

[6:5] DNM DNM

[4] IXC Inexact cumulative flag, resets to zero

[3] UFC Underflow cumulative flag, resets to zero

[2] OFC Overflow cumulative flag, resets to zero

[1] DZC Division by Zero cumulative flag, resets to zero

[0] IOC Invalid Operation cumulative flag, resets to zero

Table 12-4 FPSCR Register bit functions (continued)

Bits Field Function

Reserved

EN

Reserved

31 30 29 0

DEX

28