FPU Programmer’s Model

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 12-12

ID013010 Non-Confidential, Unrestricted Access

• In default NaN mode, arithmetic

CDP

instructions involving NaN operands return the

default NaN regardless of the fractions of any NaN operands. SNaNs in an arithmetic

CDP

operation set the IOC flag, FPSCR[0]. NaN handling by data transfer and non-arithmetic

CDP

instructions is the same as in full-compliance mode.

Table 12-9 summarizes the effects of NaN operands on instruction execution.

Comparisons

Comparison results modify the flags in the FPSCR Register. You can use the

VMOV r15, FPSCR

instruction (formerly

FMSTAT

) to transfer the current flags from the FPSCR Register to the CPSR

Register. See the ARM Architecture Reference Manual for mapping of IEEE 754 standard

predicates to ARM conditions. The flags used are chosen so that subsequent conditional

execution of ARM instructions can test the predicates defined in the IEEE 754 standard.

Underflow

The Cortex-R4F FPU uses the before rounding form of tininess and the inexact result form of

loss of accuracy as described in the IEEE 754 standard to generate Underflow exceptions.

In flush-to-zero mode, results that are tiny before rounding, as described in the IEEE 754

standard, are flushed to a zero, and the UFC flag, FPSCR[3], is set. See the ARM Architecture

Reference Manual for information on flush-to-zero mode.

When the FPU is not in flush-to-zero mode, operations are performed on subnormal operands.

If the operation does not produce a tiny result, it returns the computed result, and the UFC flag,

FPSCR[3], is not set. The IXC flag, FPSCR[4], is set if the operation is inexact. If the operation

produces a tiny result, the result is a subnormal or zero value, and the UFC flag, FPSCR[3], is

set if the result was also inexact.

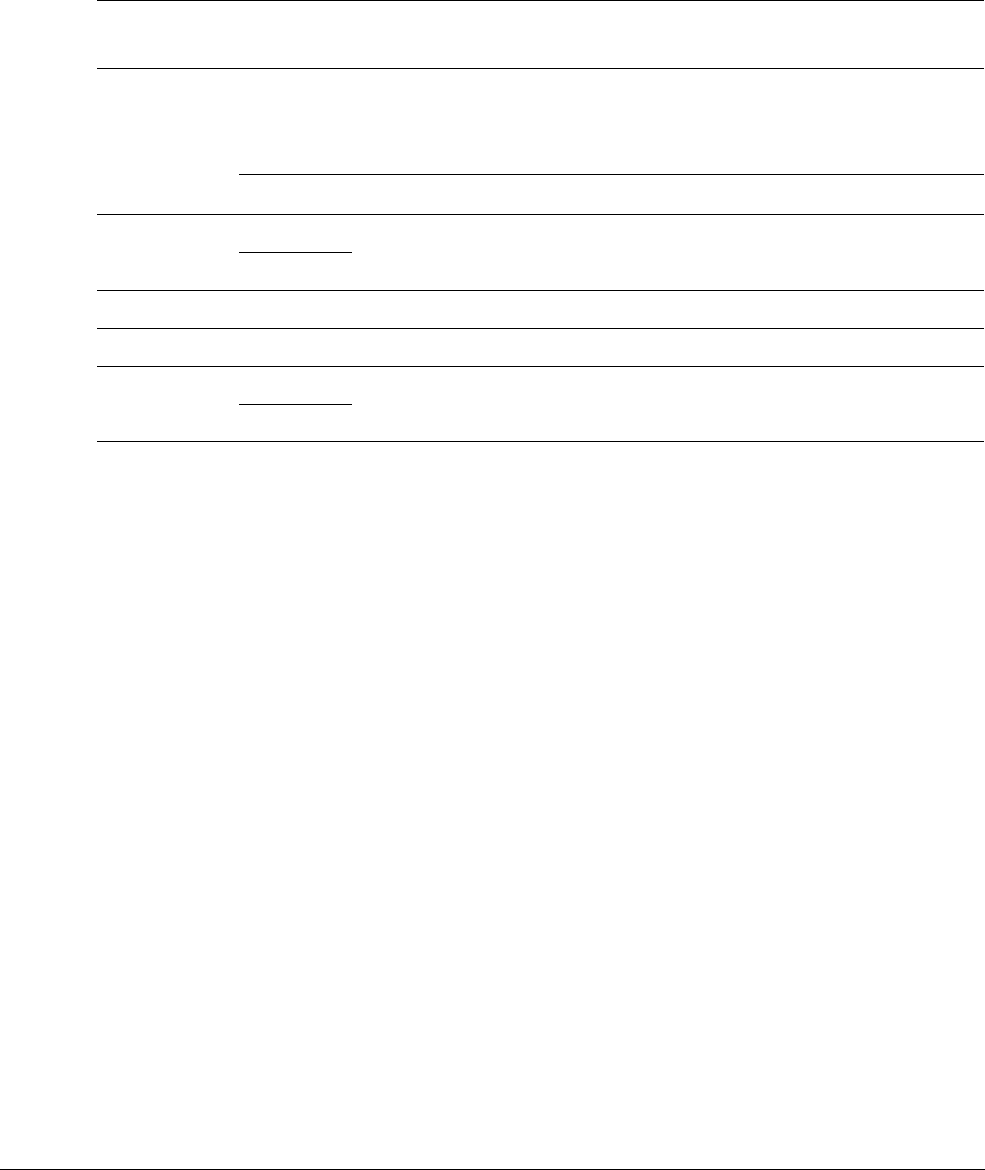

Table 12-9 QNaN and SNaN handling

Instruction

type

Default

NaN mode

With QNaN operand With SNaN operand

Arithmetic

CDP

Off The QNaN or one of the QNaN operands, if

there is more than one, is returned

according to the rules given in the ARM

Architecture Reference Manual.

IOC

a

set. The SNaN is quieted and the

result NaN is determined by the rules

given in the ARM Architecture

Reference Manual.

On Default NaN returns.

IOC

a

set. Default NaN returns.

Non-arithmetic

CDP

Off

NaN passes to destination with sign changed as appropriate.

On

FCMP(Z)

- Unordered compare. IOC set. Unordered compare.

FCMPE(Z)

- IOC set. Unordered compare. IOC set. Unordered compare.

Load/store

Off

All NaNs transferred.

On

a. IOC is the Invalid Operation exception flag, FPSCR[0].