Cycle Timings and Interlock Behavior

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 14-10

ID013010 Non-Confidential, Unrestricted Access

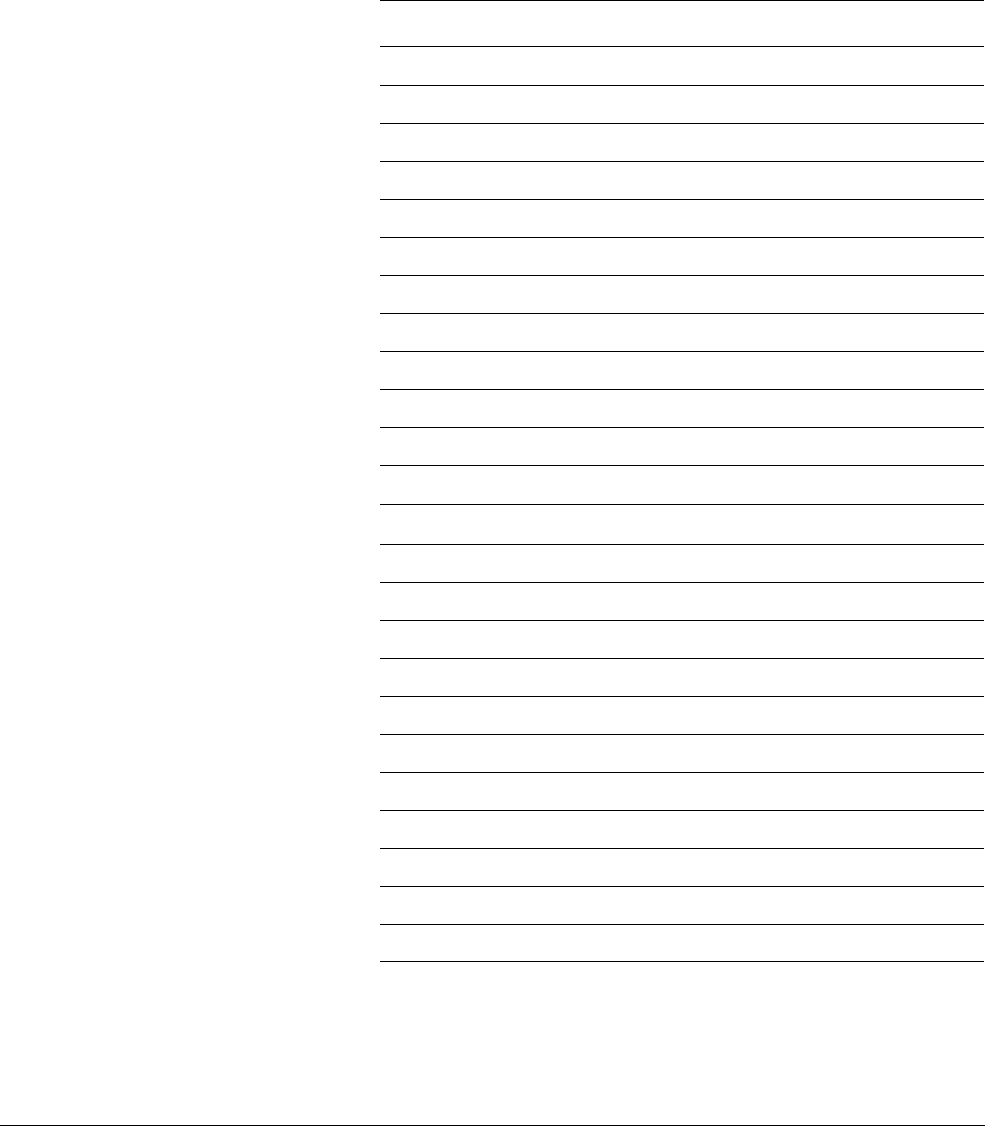

14.5 Media data-processing

Table 14-6 shows media data-processing instructions and gives their cycle timing behavior.

All media data-processing instructions are single-cycle issue instructions. These instructions

have result latencies of one or two cycles. Some of the instructions require an input register to

be shifted, or manipulated in some other way before use and therefore are marked as requiring

an Early Reg.

Table 14-6 Media data-processing instructions cycle timing behavior

Instructions Cycles Early Reg Result latency

SADD16

,

SSUB16

,

SADD8

,

SSUB8

1- 1

UADD16

,

USUB16

,

UADD8

,

USUB8

1- 1

SEL

1- 1

QADD16

,

QSUB16

,

QADD8

,

QSUB8

1- 2

SHADD16

,

SHSUB16

,

SHADD8

,

SHSUB8

1- 1

UQADD16

,

UQSUB16

,

UQADD8

,

UQSUB8

1- 2

UHADD16

,

UHSUB16

,

UHADD8

,

UHSUB8

1- 1

SSAT16

,

USAT16

1

<Rn>

1

SASX

,

SSAX

1- 1

UASX

,

USAX

1- 1

SXTAB

,

SXTAB16

,

SXTAH

1

<Rm>

1

SXTB

,

SXTB16

,

SXTH

1

<Rm>

a

a. A shift of zero makes

<Rm>

a Normal Reg for these instructions.

1

UXTB

,

UXTB16

,

UXTH

1

<Rm>

a

1

UXTAB

,

UXTAB16

,

UXTAH

1

<Rm>

1

REV

,

REV16

,

REVSH

,

RBIT

1

<Rm>

1

PKHBT

,

PKHTB

1

<Rm>

1

SSAT

,

USAT

1

<Rm>

1

QASX

,

QSAX

1- 2

SHASX

,

SHSAX

1- 1

UQASX

,

UQSAX

1- 2

UHASX

,

UHSAX

1- 1

BFC

1

<Rd>

1

SBFX

,

UBFX

1

<Rn>

1

BFI

1

<Rd>, <Rn>

1