Integration Test Registers

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 13-9

ID013010 Non-Confidential, Unrestricted Access

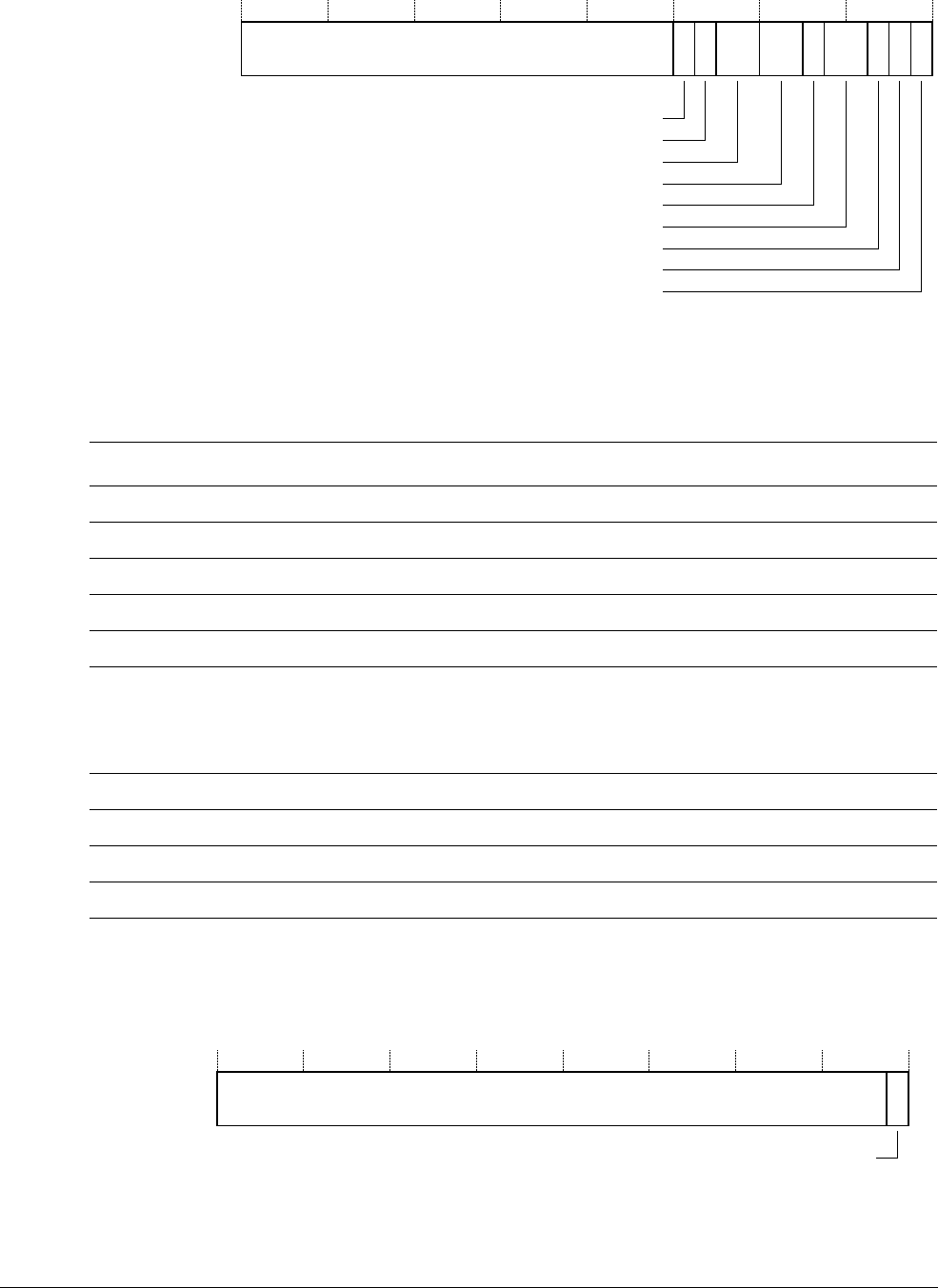

Figure 13-3 ITMISCIN Register bit assignments

Table 13-6 lists the register bit assignments for the ITMISCIN Register.

13.4.6 Integration Mode Control Register (ITCTRL)

The ITCTRL Register, register

0x3C0

at offset

0xF00

, is read/write. Figure 13-4 shows the

register bit assignments.

Figure 13-4 ITCTRL Register bit assignments

Reserved

31 10 9 8 7 4 3 2 0

ETMEXTOUT[1:0]

65

Reserved

nETMWFIREADY

Reserved

nFIQ

nIRQ

EDBGRQ

Reserved

DBGRESTART

1112 1

Table 13-6 ITMISCIN Register bit assignments

Bits Name Function

[31:12] - Reserved. Read Undefined.

[11] DBGRESTART Read value of the DBGRESTART input pin.

[10] - Reserved. Read Undefined.

[9:8] ETMEXTOUT Read value of the ETMEXTOUT[1:0] input pins.

[7:6] - Reserved. Read Undefined.

[5] nETMWFIREADY Reads the nETMWFIREADY input pin. Although this pin is active LOW, the value of

this bit matches the physical state of the signal:

0 = input pin is LOW (asserted)

1 = input pin is HIGH (deasserted).

[4:3] - Reserved. Read Undefined.

[2] nFIQ Read value of nFIQ input pin.

[1] nIRQ Read value of nIRQ input pin.

[0] EDBGRQ Read value of EDBGRQ input pin.

Reserved

31 0

1

INTMODE