Clock Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 6-11

6.7.1.3 Relaxation Oscillator Control Register (ROCR)

The ROCR is used to trim the frequency of the on-chip oscillator. Setting one of the TRIM bits engages

its associated bypass capacitance, which increases or decreases the period of the output frequency. The

largest capacitance, and thus the biggest frequency step (40%), is associated with TRIM9. The lowest

capacitance, and thus the smallest frequency step (0.8%), is associated with TRIM0. The tuning steps are

binary-weighted in terms of signal period, not frequency. The module was designed such that the

approximate middle of the tuning range is 8 MHz.

6.7.1.4 Low-Power Divider Register (LPDR)

The LPDR contains a 4-bit field that divides down the system clock (regardless if the reference clock or

PLL clock is driving the system clock) by a factor of 2

n

(where n is a number from 0 to 15 represented by

the 4 bit field). The clock change takes effect with the next rising edge of the system clock.

IPSBAR

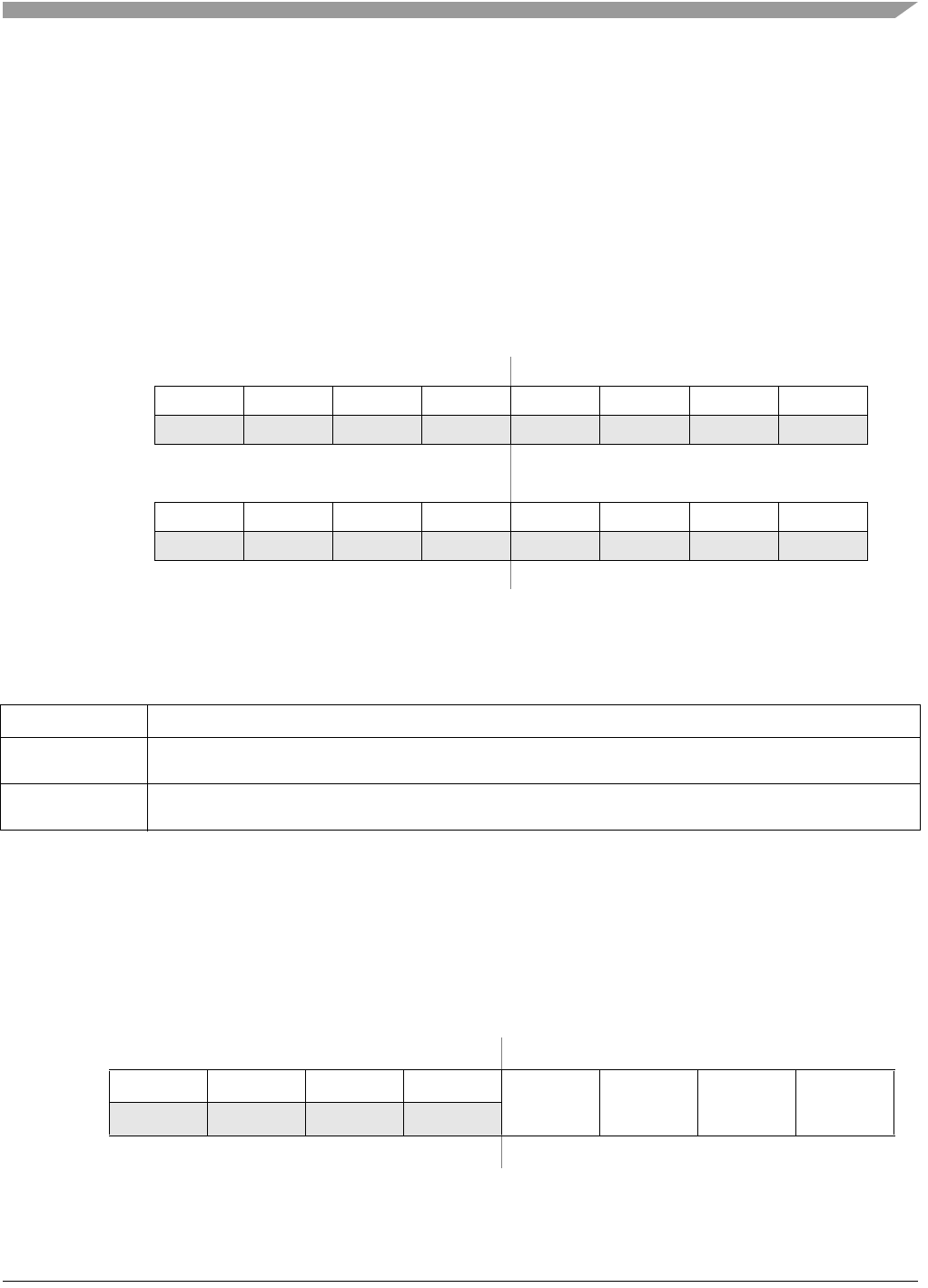

Offset: 0x12_0004 (ROCR)

Access: Supervisor read/write

15 14 13 12 11 10 9 8

R——————TRIM9TRIM8

W

Reset000000See note

1

1

Loaded during reset from the flash information row (bits [9:0]).

See note 1

76543210

R TRIM7 TRIM6 TRIM5 TRIM4 TRIM3 TRIM2 TRIM1 TRIM0

W

Reset See note 1 See note 1 See note 1 See note 1 See note 1 See note 1 See note 1 See note 1

Figure 6-4. Relaxation Oscillator Control Register (ROCR)

Table 6-7. ROCR Field Descriptions

Field Description

15–10

—

Reserved, should be cleared.

9–0

TRIM

10-bit trim value used to trim the frequency of the on-chip oscillator.

IPSBAR

Offset: 0x12_0007 (LPDR)

Access: Supervisor read/write

76543210

R — — — —

LPD3 LPD2 LPD1 LPD0

W

Reset:00000000

Figure 6-5. Low-Power Divider Register (LPDR)