DMA Controller Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

17-6 Freescale Semiconductor

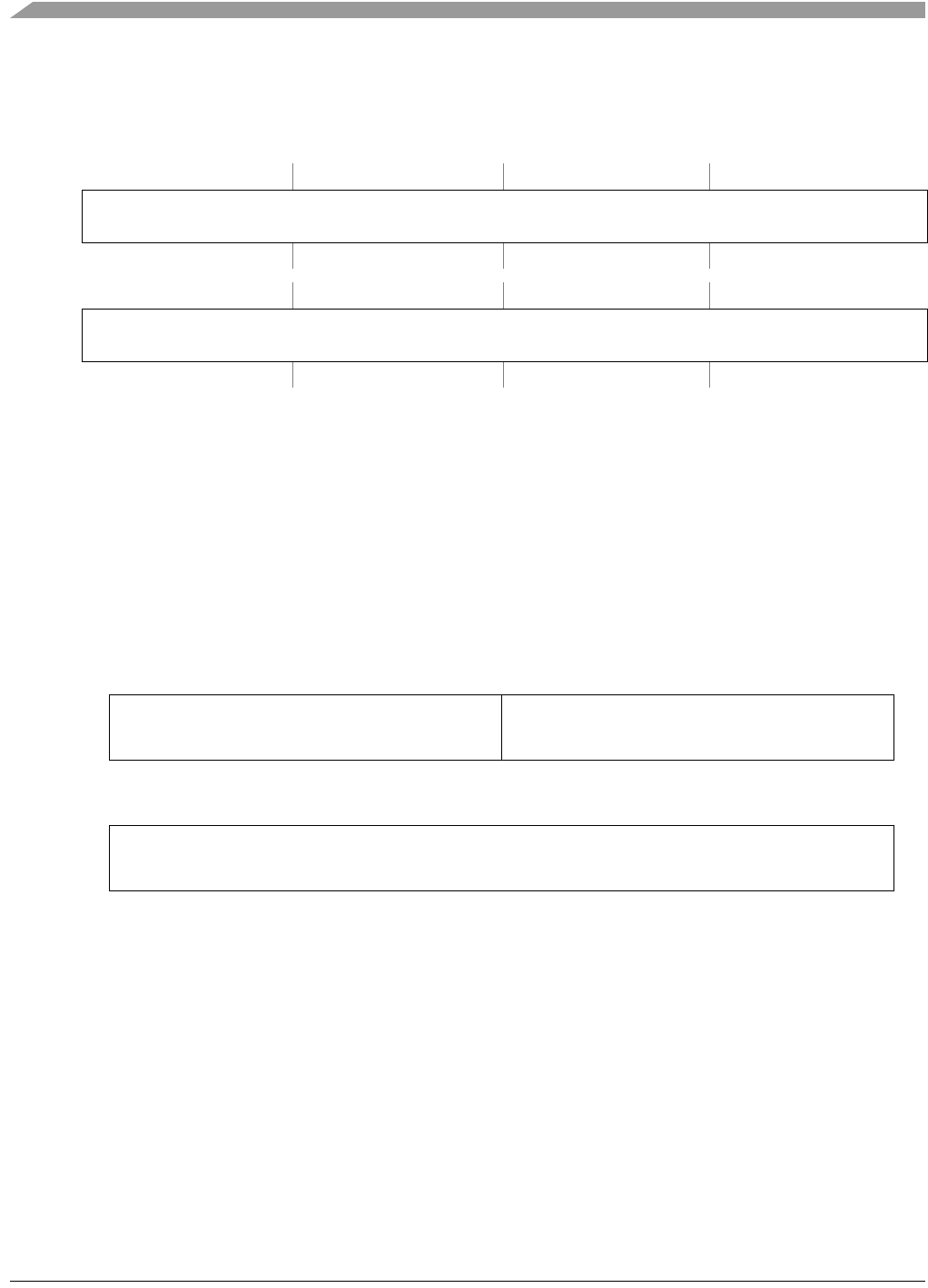

17.3.4 Byte Count Registers (BCRn) and DMA Status Registers (DSRn)

The Byte Count Registers (BCRn) and DMA Status Registers (DSRn) are two logical registers that occupy

one 32-bit register, as shown in Figure 17-6. The address used to access both registers is the same; DSRn

occupies bits 31–24, and BCRn occupies bits 23–0.

BCRn contains the number of bytes yet to be transferred for a given block. BCRn decrements on the

successful completion of the address transfer of a write transfer. BCRn decrements by 1, 2, 4, or 16 for

byte, word, longword, or line accesses, respectively.

The fields of the DSRn register (bits 31–24 in Figure 17-6) are shown in Figure 17-7. In response to an

event, the DMA controller writes to the appropriate DSRn bit. Only a write to DSRn[DONE] results in

action. DSRn[DONE] is set when the block transfer is complete.

When a transfer sequence is initiated and BCRn[BCR] is not a multiple of 16, 4, or 2 when the DMA is

configured for line, longword, or word transfers, respectively, DSRn[CE] is set and no transfer occurs.

IPSBAR

Offsets:

0x00_0104 (DAR0)

0x00_0114 (DAR1)

0x00_0124 (DAR2)

0x00_0134 (DAR3)

Access: read/write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

DAR

W

Reset00000000000000 0 0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

DAR

W

Reset00000000000000 0 0

Figure 17-5. Destination Address Registers (DARn)

IPSBAR

Offsets:

0x00_0108 (BCR0/DSR0)

0x00_0118 (BCR1/DSR1)

0x00_0128 (BCR2/DSR2)

0x00_0138 (BCR3/DSR3)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

DSR BCR

W

Reset0000000000000000

1514131211109876543210

R

BCR

W

Reset0000000000000000

Figure 17-6. Byte Count Registers (BCRn) and DMA Status Registers (DSRn)