Debug Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

28-16 Freescale Semiconductor

contents of the breakpoint registers are compared with the processor’s program counter register when TDR

is configured appropriately.

The PC breakpoint registers are accessible in supervisor mode using the WDEBUG instruction and

through the BDM port using the WDMREG command using values shown in Section 28.5.3.3, “Command

Set Descriptions”.

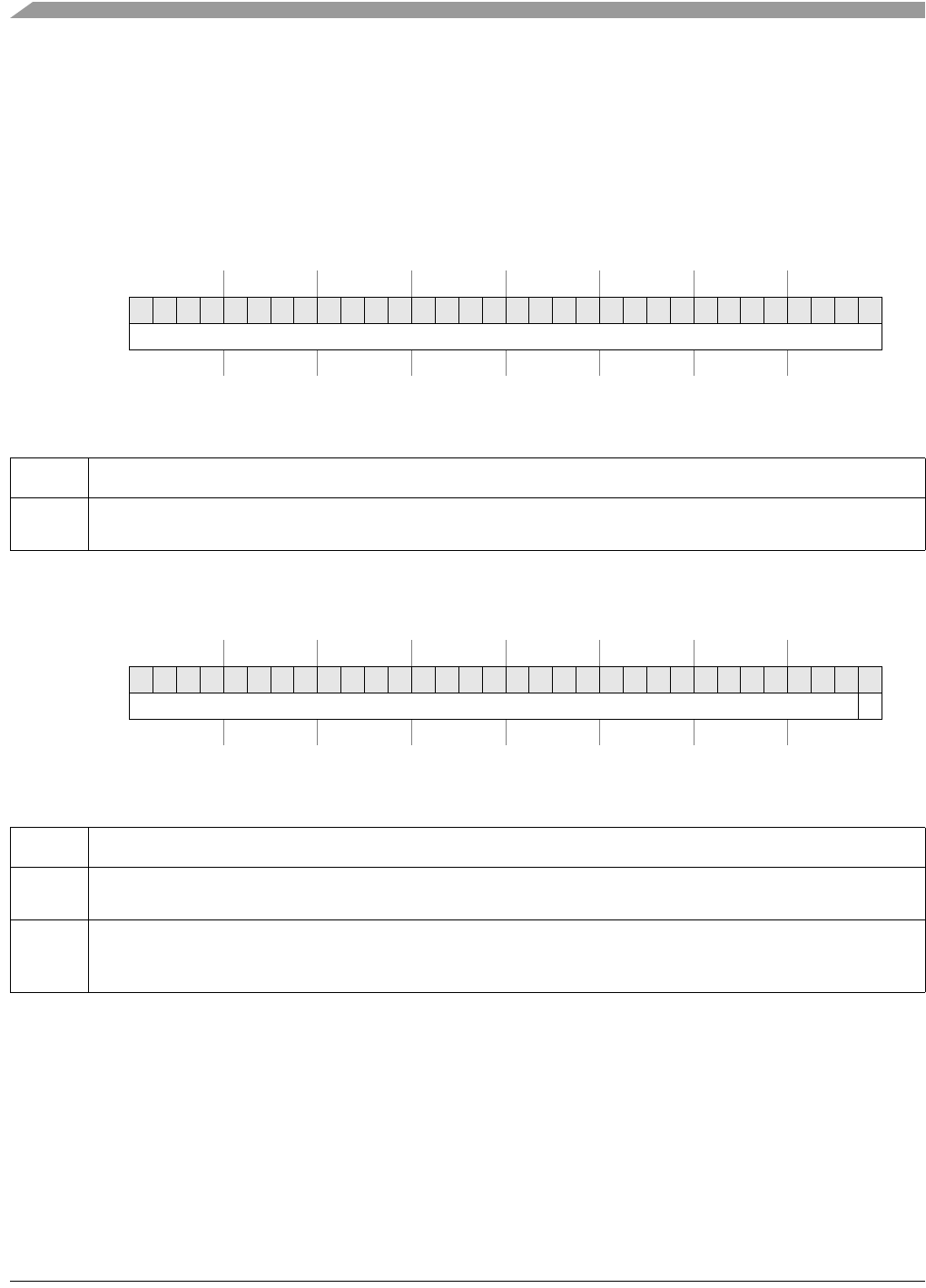

Figure 28-9 shows PBMR. PBMR is accessible in supervisor mode using the WDEBUG instruction and

via the BDM port using the WDMREG command. PBMR only masks PBR0.

DRc[4:0]: 0x08 (PBR0) Access: Supervisor write-only

BDM write-only

313029282726252423222120191817161514131211109876543210

R

WAddress

Reset––––––––––––––––––––––––––––––––

Figure 28-7. PC Breakpoint Register (PBR0)

Table 28-10. PBR0 Field Descriptions

Field Description

31–0

Address

PC Breakpoint Address. The address to be compared with the PC as a breakpoint trigger.

Note: PBR0[0] should always be loaded with a 0.

DRc[4:0]: 0x18 (PBR1)

0x1A (PBR2)

0x1B (PBR3)

Access: Supervisor write-only

BDM write-only

313029282726252423222120191817161514131211109876543210

R

W Address V

Reset–––––––––––––––––––––––––––––000

Figure 28-8. PC Breakpoint Register n (PBRn)

Table 28-11. PBRn Field Descriptions

Field Description

31–1

Address

PC Breakpoint Address. The 31-bit address to be compared with the PC as a breakpoint trigger.

0

V

Valid Bit. This bit must be set for the PC breakpoint to occur at the address specified in the Address field.

0 PBR is disabled.

1 PBR is enabled.