ColdFire Core

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 3-23

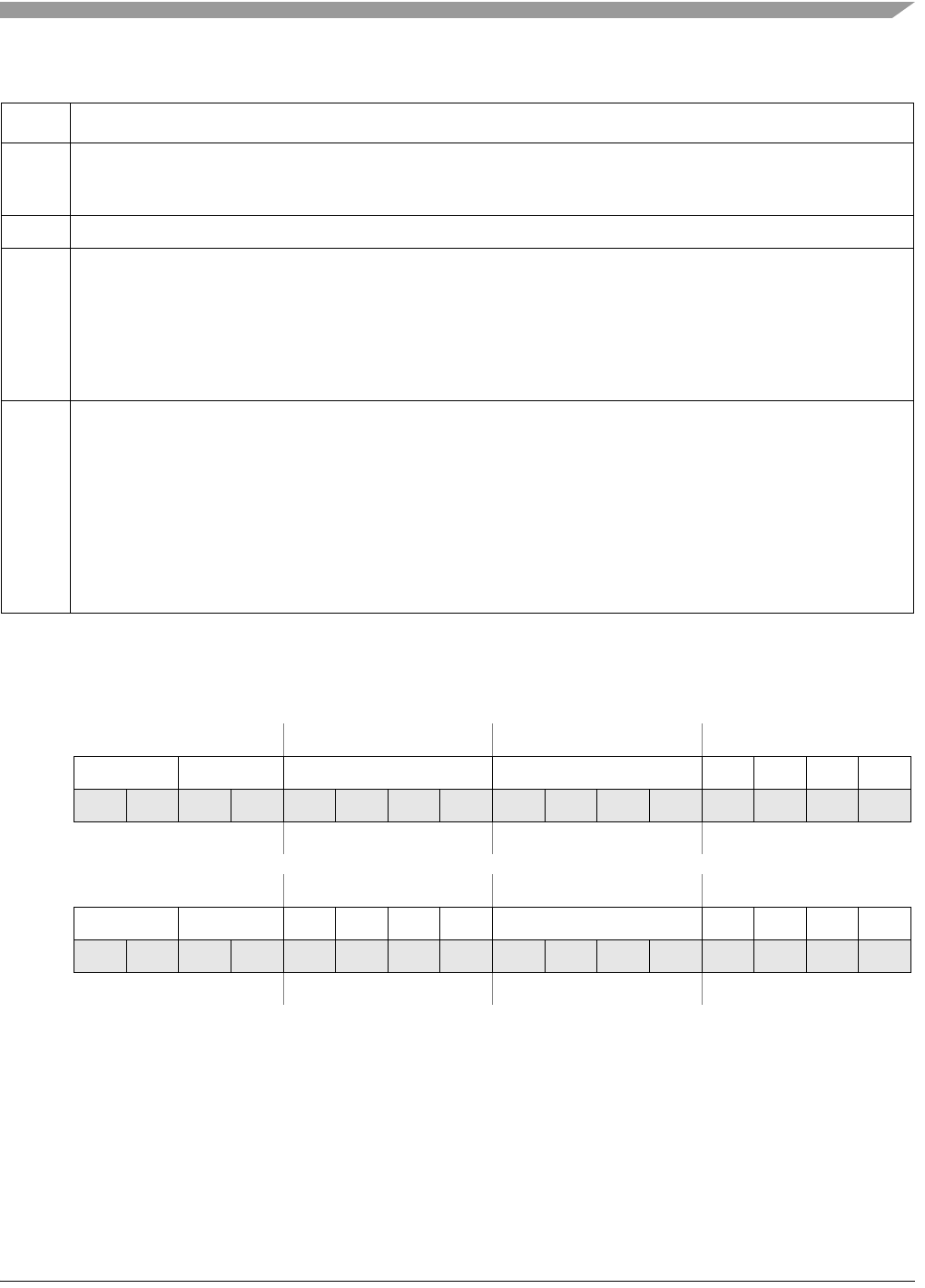

Information loaded into D1 defines the local memory hardware configuration as shown in the figure below.

11

MMU

MMU present. This bit signals if the optional virtual memory management unit (MMU) is present in processor core.

0 MMU execute engine not present in core. (This is the value used for this device.)

1 MMU execute engine is present in core.

10–8 Reserved.

7–4

ISA

ISA revision. This 4-bit field defines the instruction-set architecture (ISA) revision level implemented in ColdFire

processor core.

0000 ISA_A

0001 ISA_B

0010 ISA_C

1000 ISA_A+ (This is the value used for this device.)

Else Reserved

3–0

DEBUG

Debug module revision number. This 4-bit field defines revision level of the debug module used in the ColdFire

processor core.

0000 DEBUG_A

0001 DEBUG_B

0010 DEBUG_C

0011 DEBUG_D

0100 DEBUG_E

1001 DEBUG_B+ (This is the value used for this device.)

1011 DEBUG_D+

Else Reserved

BDM: Load: 0x081 (D1)

Store: 0x181 (D1)

Access: User read-only

BDM read-only

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RCLSZ CCAS CCSZ FLASHSZ 0000

W

Reset0001000010100000

1514131211109876543210

RMBSZ UCAS 0000 SRAMSZ 0000

W

Reset0001000001110000

Figure 3-19. D1 Hardware Configuration Info

Table 3-9. D0 Hardware Configuration Info Field Description (continued)

Field Description