General Purpose Timer Module (GPT)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 21-5

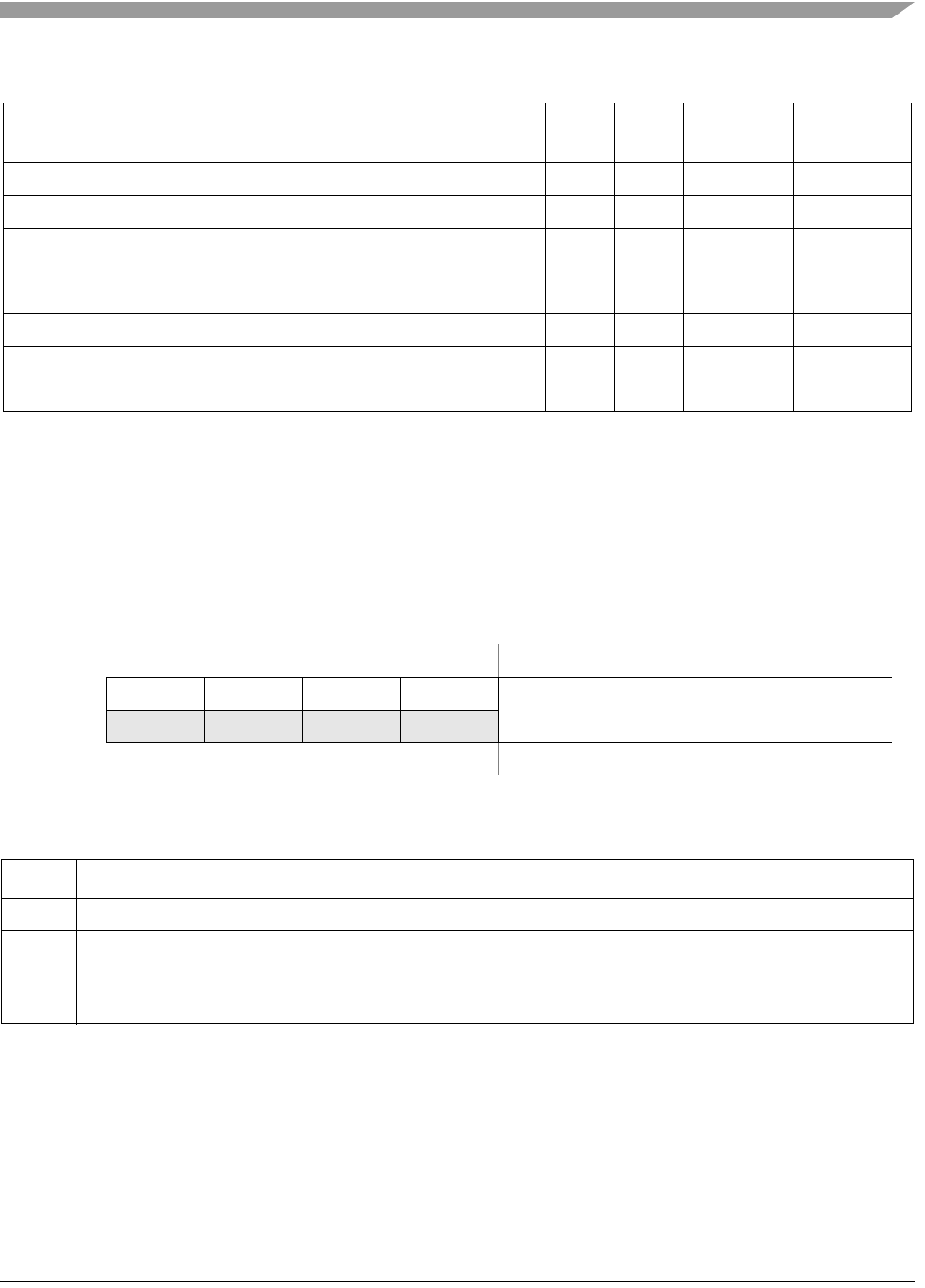

21.6.1 GPT Input Capture/Output Compare Select Register (GPTIOS)

0x1A_0017 GPT Channel 3 Register Low (GPTC3L)

2

8 21.6.14/21-13

0x1A_0018 Pulse Accumulator Control Register (GPTPACTL) 8 R/W 0x00 21.6.15/21-13

0x1A_0019 Pulse Accumulator Flag Register (GPTPAFLG) 8 R/W 0x00 21.6.16/21-14

0x1A_001A Pulse Accumulator Counter Register High

(GPTPACNTH)

2

8R/W 21.6.17/21-15

0x1A_001B Pulse Accumulator Counter Register Low (GPTPACNTL)

2

8R/W 21.6.17/21-15

0x1A_001D GPT Port Data Register (GPTPORT) 8 R/W 0x00 21.6.18/21-16

0x1A_001E GPT Port Data Direction Register (GPTDDR) 8 R/W 0x00 21.6.19/21-16

1

Addresses not assigned to a register and undefined register bits are reserved for expansion.

2

This register is 16 bits wide, and should be read using only word accesses.

IPSBAR

Offset: 0x1A_0000 (GPTIOS)

Access: Supervisor read/write

76543210

R 0 0 0 0

IOS

W

Reset:00000000

Figure 21-2. GPT Input Capture/Output Compare Select Register (GPTIOS)

Table 21-4. GPTIOS Field Descriptions

Field Description

7–4 Reserved, should be cleared.

3–0

IOS

I/O select. The IOS[3:0] bits enable input capture or output compare operation for the corresponding timer channels.

These bits are read anytime (always read 0x00), write anytime.

1 Output compare enabled

0 Input capture enabled

Table 21-3. GPT Memory Map (continued)

IPSBAR

Offset

1

Register

Width

(bits)

Access Reset Value Section/Page