Pulse-Width Modulation (PWM) Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 27-5

27.2.4 PWM Prescale Clock Select Register (PWMPRCLK)

The PWMPRCLK register selects the prescale clock source for clocks A and B independently. If the clock

prescale is changed while a PWM signal is being generated, a truncated or stretched pulse can occur during

the transition.

IPSBAR

Offset:

0x1B_0002 (PWMCLK) Access: User Read/Write

76543210

R

PCLK7 PCLK6 PCLK5 PCLK4 PCLK3 PCLK2 PCLK1 PCLK0

W

Reset:00000000

Figure 27-4. PWM Clock Select Register (PWMCLK)

Table 27-4. PWMCLK Field Descriptions

Field Description

7–0

PCLKn

PWM channel n clock select. Selects between one of two clock sources for each PWM channel. See Section 27.2.4,

“PWM Prescale Clock Select Register (PWMPRCLK)” and Section 27.2.7, “PWM Scale A Register (PWMSCLA)” for

more information on how the different clock rates are generated. The even-numbered channels’ clock select has no

effect when the corresponding PWMCTL[CONn(n+1)] bit is set. For example, if PWMCTL[CON01] equals 1,

PWMCLK[PCLK0] has no affect.

IPSBAR

Offset:

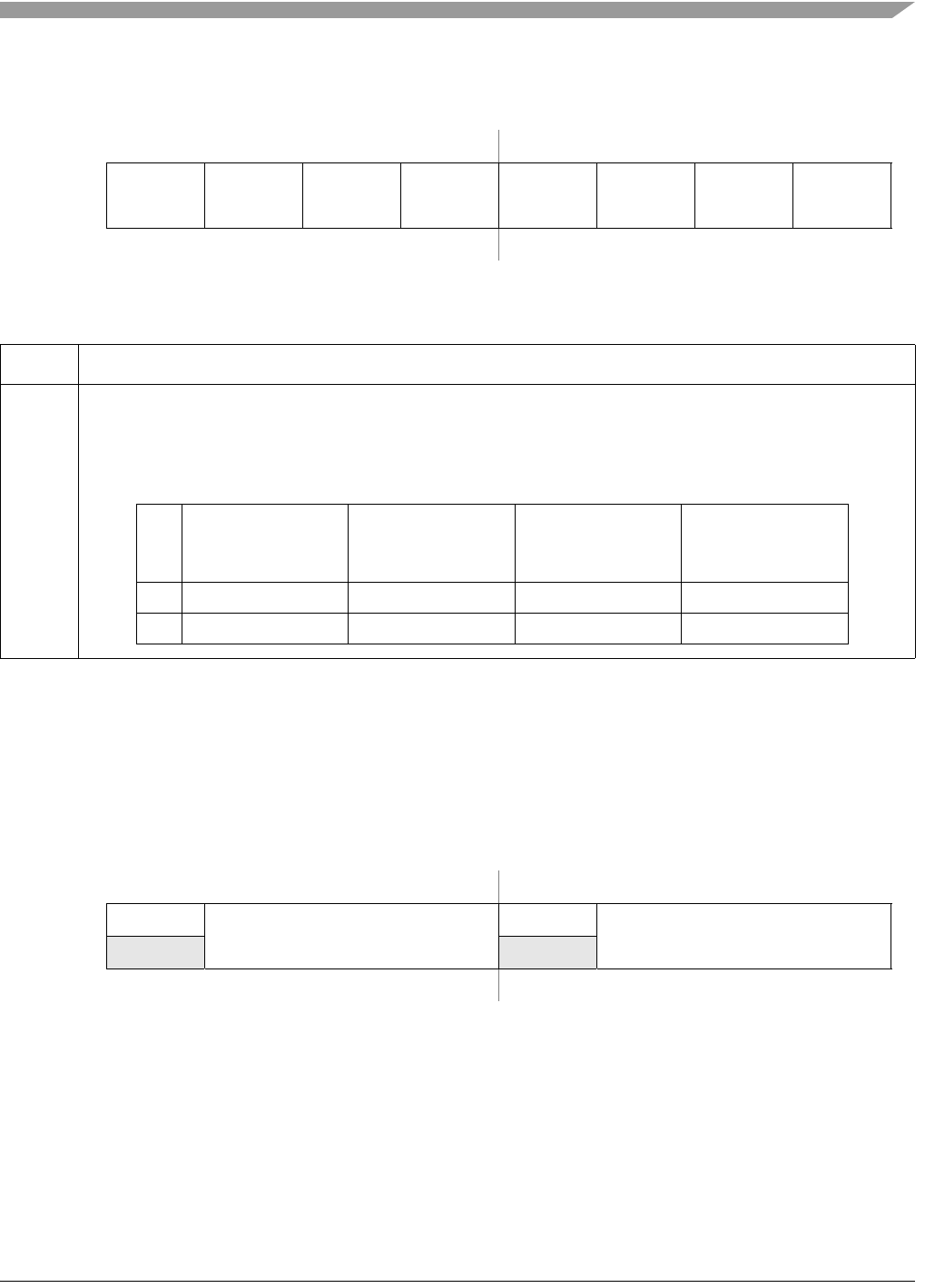

0x1B_0003 (PWMPRCLK) Access: User Read/Write

76543210

R 0

PCKB

0

PCKA

W

Reset:00000000

Figure 27-5. PWM Prescale Clock Select Register (PWMPRCLK)

PCLK6 & PCLK7

(PWM6 & PWM7

Clock Source)

PCLK4 & PCLK5

(PWM4 & PWM5

Clock Source)

PCLK2 & PCLK3

(PWM2 & PWM3

Clock Source)

PCLK0 & PCLK1

(PWM0 & PWM1

Clock Source)

0BABA

1SBSASBSA