MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 8-1

Chapter 8

Power Management

8.1 Introduction

This chapter explains the low-power operation of the MCF52211.

8.1.1 Features

The following features support low-power operation.

• Four modes of operation: run, wait, doze, and stop

• Ability to shut down most peripherals independently

• Ability to shut down the external CLKOUT pin

8.2 Memory Map/Register Definition

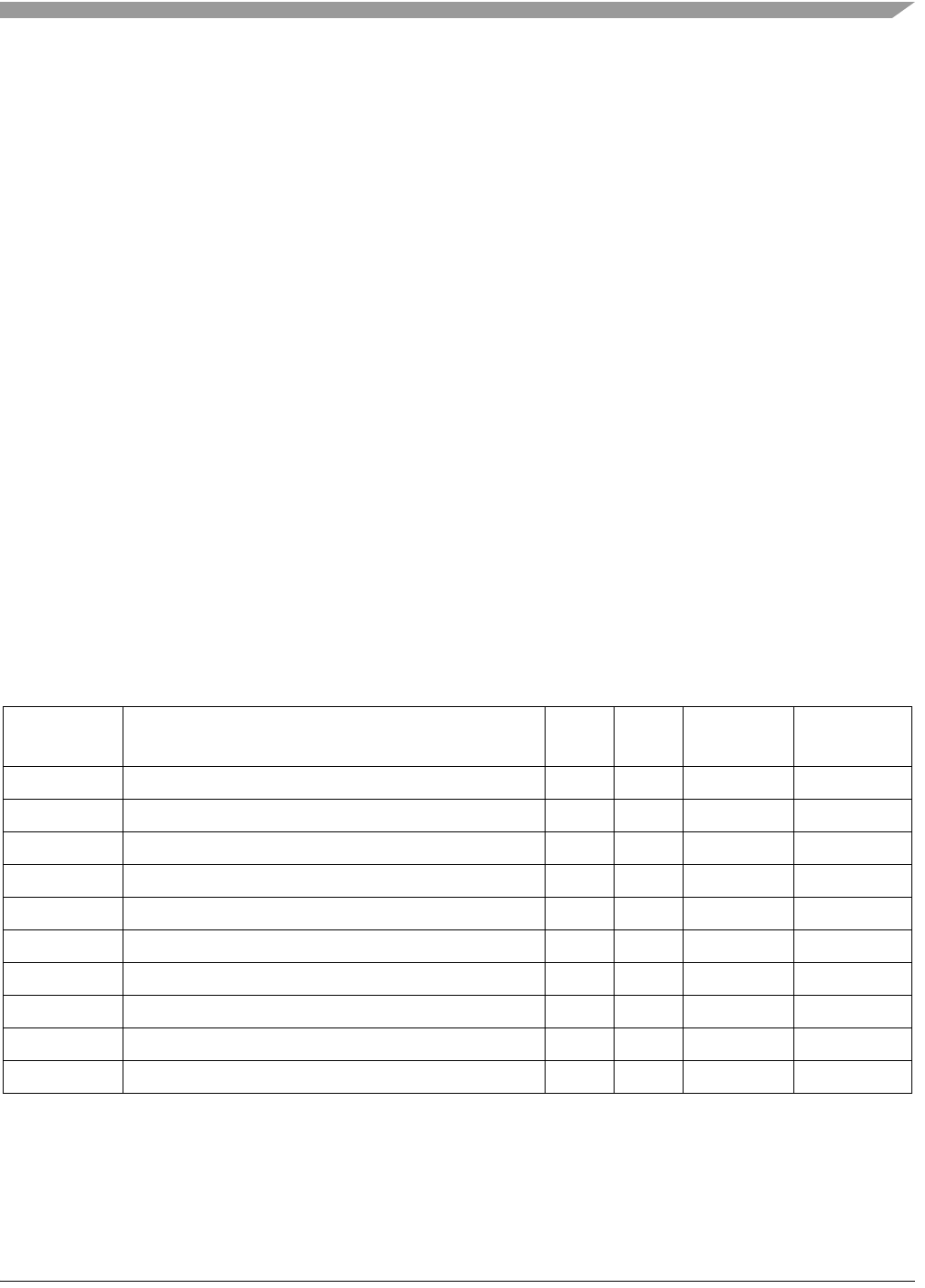

The power management programming model consists of registers from the SCM and CCM memory space,

as shown in Table 8-1.

Table 8-1. Power Management Memory Map

IPSBAR

Offset

1

1

Addresses not assigned to a register and undefined register bits are reserved for expansion.

Register

Width

(bits)

Access Reset Value Section/Page

0x11_0004 Chip Configuration Register (CCR)

2

2

The CCR is described in the Chip Configuration Module. It is shown here only to warn against accidental writes to this register

when accessing the LPCR.

16 R 0x1 9.3.3.1/9-3

0x11_0007 Low-Power Control Register (LPCR) 8 R/W 0x2 8.2.5/8-8

0x00_000C Peripheral Power Management Register High (PPMRH) 32 R/W 0x0 8.2.1/8-2

0x00_0010 Core Reset Status Register (CRSR)

3

3

The CRSR, CWCR, and CWSR are described in the System Control Module. They are shown here only to warn against

accidental writes to these registers when accessing the LPICR.

8R/W 12.5.3/12-6

0x00_0011 Core Watchdog Control Register (CWCR)

3

8R/W 0x0 12.5.4/12-7

0x00_0012 Low-Power Interrupt Control Register (LPICR) 8 R/W 0x0 8.2.2/8-5

0x00_0013 Core Watchdog Service Register (CWSR)

3

8R/W 12.5.5/12-8

0x00_0018 Peripheral Power Management Register Low (PPMRL) 32 R/W 0x8 8.2.1.1/8-4

0x00_0021 Peripheral Power Management Set Register (PPMRS) 8 W 0x0 8.2.3/8-7

0x00_0022 Peripheral Power Management Clear Register (PPMRC) 32 R/W 0x0 8.2.4/8-8