General Purpose I/O Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 13-15

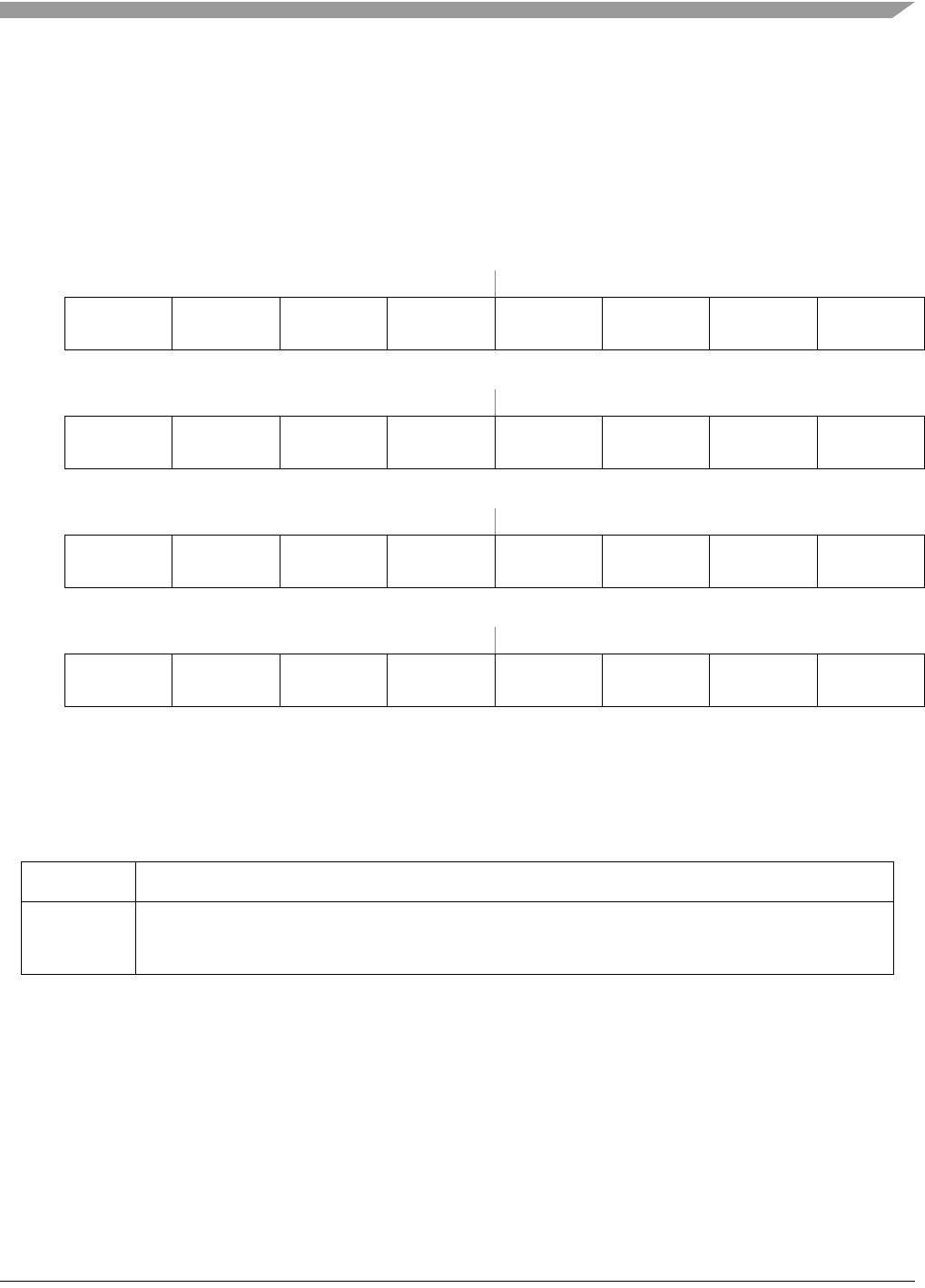

13.6.6.2 Pin Drive Strength Register (PDSR)

The pin drive strength register is read/write. Each bit resets to logic 0 in single chip mode (MCF52211

default) and logic 1 in EzPort and FAST mode. The fields are described in Table 13-9.

Refer to Table 2-1 for details of which PDSR bit controls which pin.

.

13.7 Ports Interrupts

The ports module does not generate interrupt requests.

IPSBAR

Offset: 0x10_007C (PDSR)

Access: User read/write

31 30 29 28 27 26 25 24

R

PDSR31 PDSR30 PDSR29 PDSR28 PDSR27 PDSR26 PDSR25 PDSR24

W

Reset See note 1

23 22 21 20 19 18 17 16

R

PDSR23 PDSR22 PDSR21 PDSR20 PDSR19 PDSR18 PDSR17 PDSR16

W

Reset See note 1

15 14 13 12 11 10 9 8

R

PDSR15 PDSR14 PDSR13 PDSR12 PDSR11 PDSR10 PDSR9 PDSR8

W

Reset See note 1

76543210

R

PDSR7 PDSR6 PDSR5 PDSR4 PDSR3 PDSR2 PDSR1 PDSR0

W

Reset See note 1

1)Each bit resets to logic 0 in Single Chip mode and logic 1 in EzPort/FAST mode.

Figure 13-29. Pin Drive Strength Register (PDSR)

Table 13-9. PDSR Field Descriptions

Field Description

PDSRx PDSRx pin strength register control bits.

1 Pin is configured for high drive strength (10mA)

0 Pin is configured for low drive strength (2mA)