Interrupt Controller Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

14-10 Freescale Semiconductor

14.3.4 Interrupt Request Level Register (IRLRn)

This 7-bit register is updated each machine cycle and represents the current interrupt requests for each

interrupt level, where bit 7 corresponds to level 7, bit 6 to level 6, etc.

14.3.5 Interrupt Acknowledge Level and Priority Register (IACKLPRn)

Each time an IACK is performed, the interrupt controller responds with the vector number of the highest

priority source within the level being acknowledged. In addition to providing the vector number directly

for the byte-sized IACK read, this 8-bit register is also loaded with information about the interrupt level

and priority being acknowledged. This register provides the association between the acknowledged

physical interrupt request number and the programmed interrupt level/priority. The contents of this

read-only register are described in Figure 14-8 and Table 14-10.

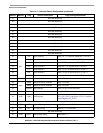

IPSBAR

Offset: 0x0C18 (IRLRn)

Access: Read-only

76543210

R IRQ[7:1] 0

W

Reset:00000000

Figure 14-7. Interrupt Request Level Register (IRLRn)

Table 14-9. IRLRn Field Descriptions

Field Description

7–1

IRQ

Interrupt requests. Represents the prioritized active interrupts for each level.

0 There are no active interrupts at this level

1 There is an active interrupt at this level

0 Reserved

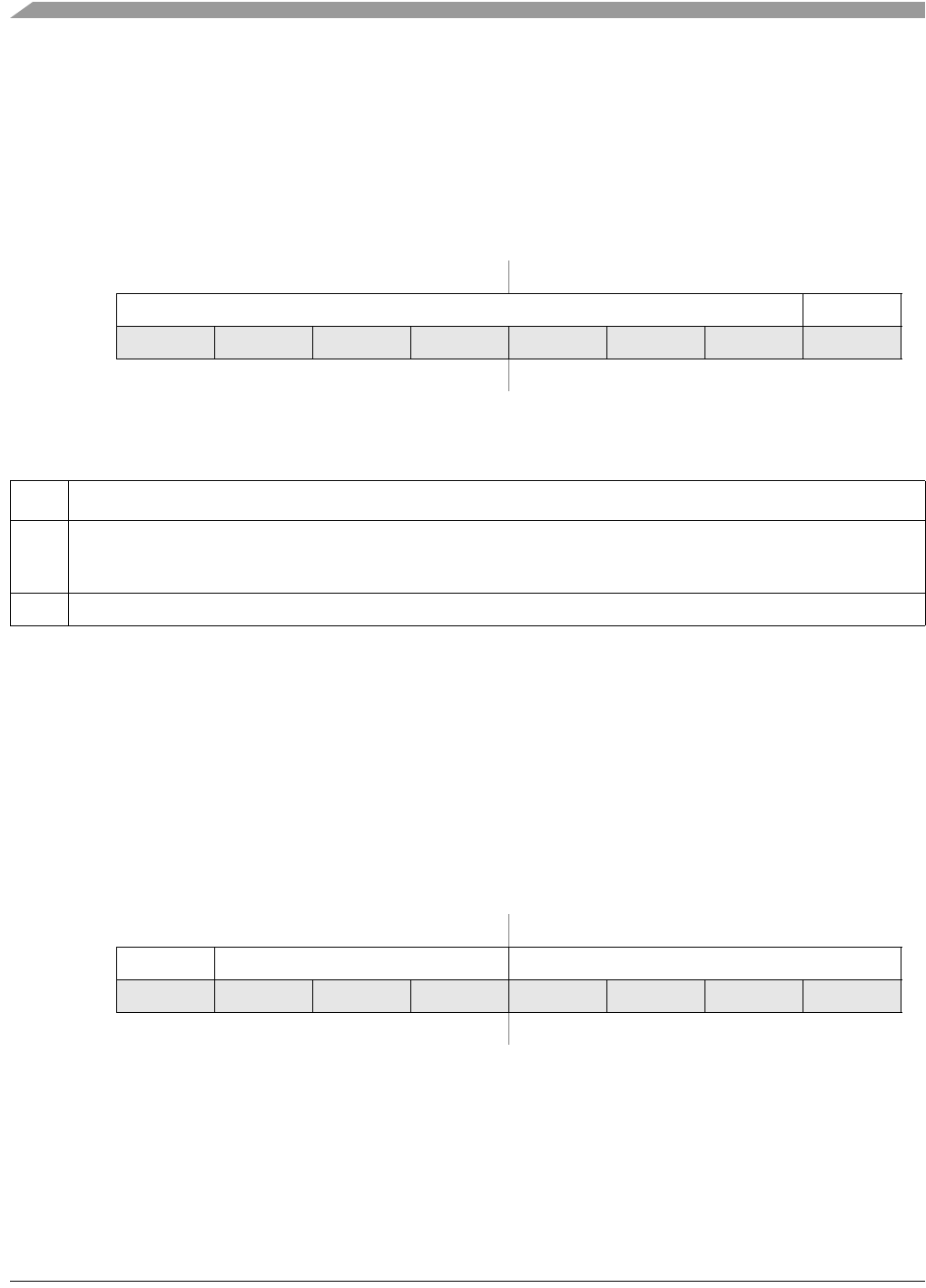

IPSBAR

Offset: 0x0C19 (IACKLPRn)

Access: Read-only

76543210

R 0 LEVEL PRI

W

Reset:00000000

Figure 14-8. IACK Level and Priority Register (IACKLPRn)