General Purpose I/O Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 13-13

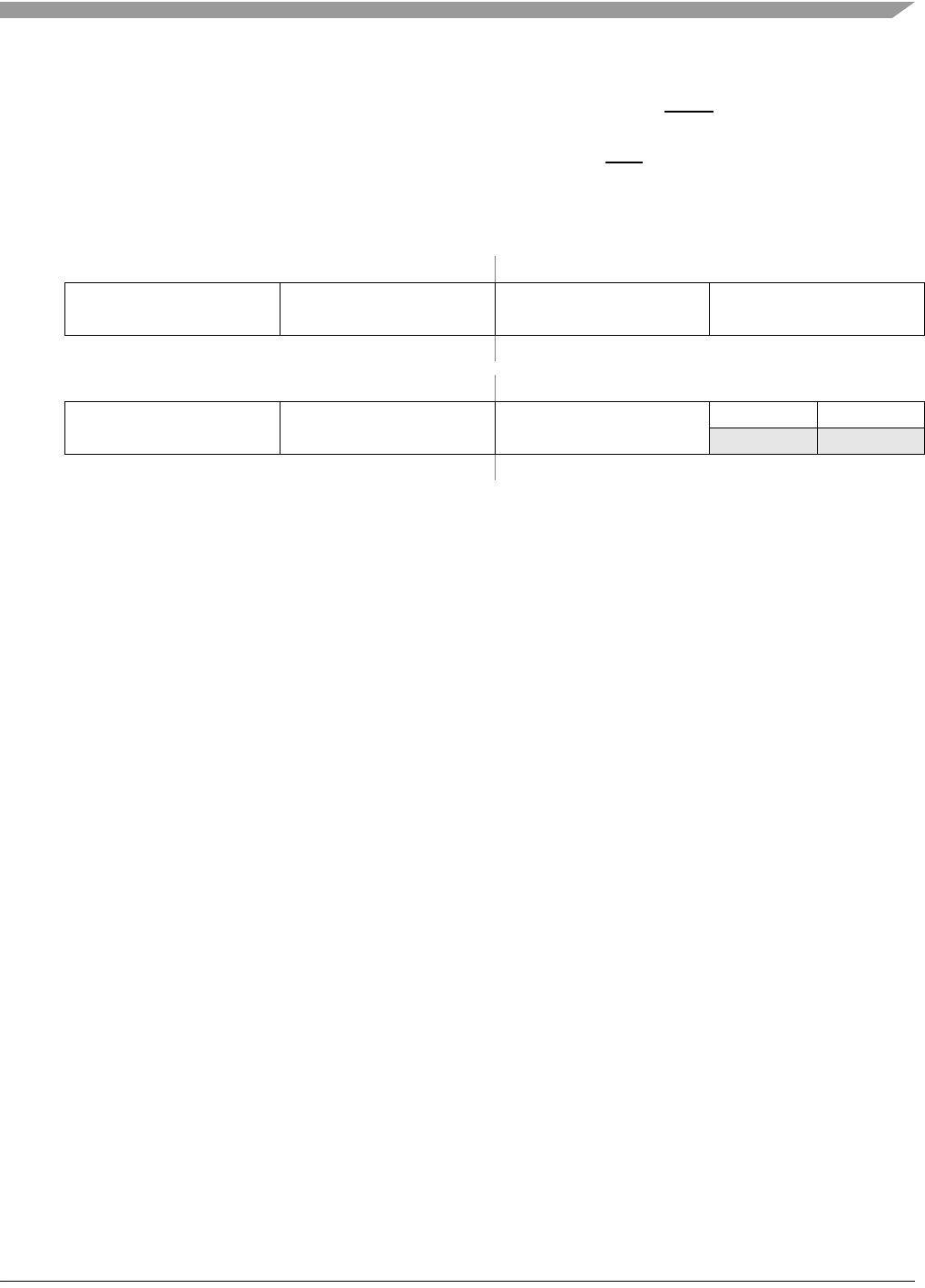

13.6.5.3 Port NQ Pin Assignment Register (PNQPAR)

The port NQ pin assignment register (PNQPAR) contains quad-function (for IRQ1) and dual-function pin

assignment controls. Refer to Table 13-6 and Table 13-7 for the encodings for the different fields. The

reset value of the PNQPAR register defaults to the primary function (IRQ) instead of GPIO.

13.6.6 Pad Control Registers

13.6.6.1 Pin Slew Rate Register (PSRR)

The pin slew rate register (PSRR) is read/write. Each bit resets to logic 0 in Single Chip mode (MCF52211

default) and logic 1 in EzPort and FAST mode. The fields are described in Table 13-8.

The slew rate control bits corresponding to each pin/signal are listed in Table 2-1.

IPSBAR

Offset: 0x10_0068 (PNQPAR)

Access: User read/write

15 14 13 12 11 10 9 8

R

PNQPAR7 PNQPAR6 PNQPAR5 PNQPAR4

W

Reset010100101

76543210

R

PNQPAR3 PNQPAR2 PNQPAR1

0 0

W

Reset01010100

Figure 13-27. Port NQ Pin Assignment Register (PNQPAR)