Queued Serial Peripheral Interface (QSPI)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

23-8 Freescale Semiconductor

23.3.6 QSPI Data Register (QDR)

The QDR is used to access QSPI RAM indirectly. The CPU reads and writes all data from and to the QSPI

RAM through this register.

A write to QDR causes data to be written to the RAM entry specified by QAR[ADDR]. This also causes

the value in QAR to increment. Correspondingly, a read at QDR returns the data in the RAM at the address

specified by QAR[ADDR]. This also causes QAR to increment. A read access requires a single wait state.

23.3.7 Command RAM Registers (QCR0–QCR15)

The command RAM is accessed using the upper byte of the QDR; the QSPI cannot modify information in

command RAM. There are 16 bytes in the command RAM. Each byte is divided into two fields. The chip

select field enables external peripherals for transfer. The command field provides transfer operations.

IPSBAR

Offset:

0x00_0350 (QAR) Access: User read/write

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R0000000000

ADDR

W

Reset0000000000000000

Figure 23-7. QSPI Address Register (QAR)

Table 23-7. QAR Field Descriptions

Field Description

15–6 Reserved, should be cleared.

5–0

ADDR

Address used to read/write the QSPI RAM. Ranges are as follows:

0x00–0x0F Transmit RAM

0x10–0x1F Receive RAM

0x20–0x2F Command RAM

0x30–0x3F Reserved

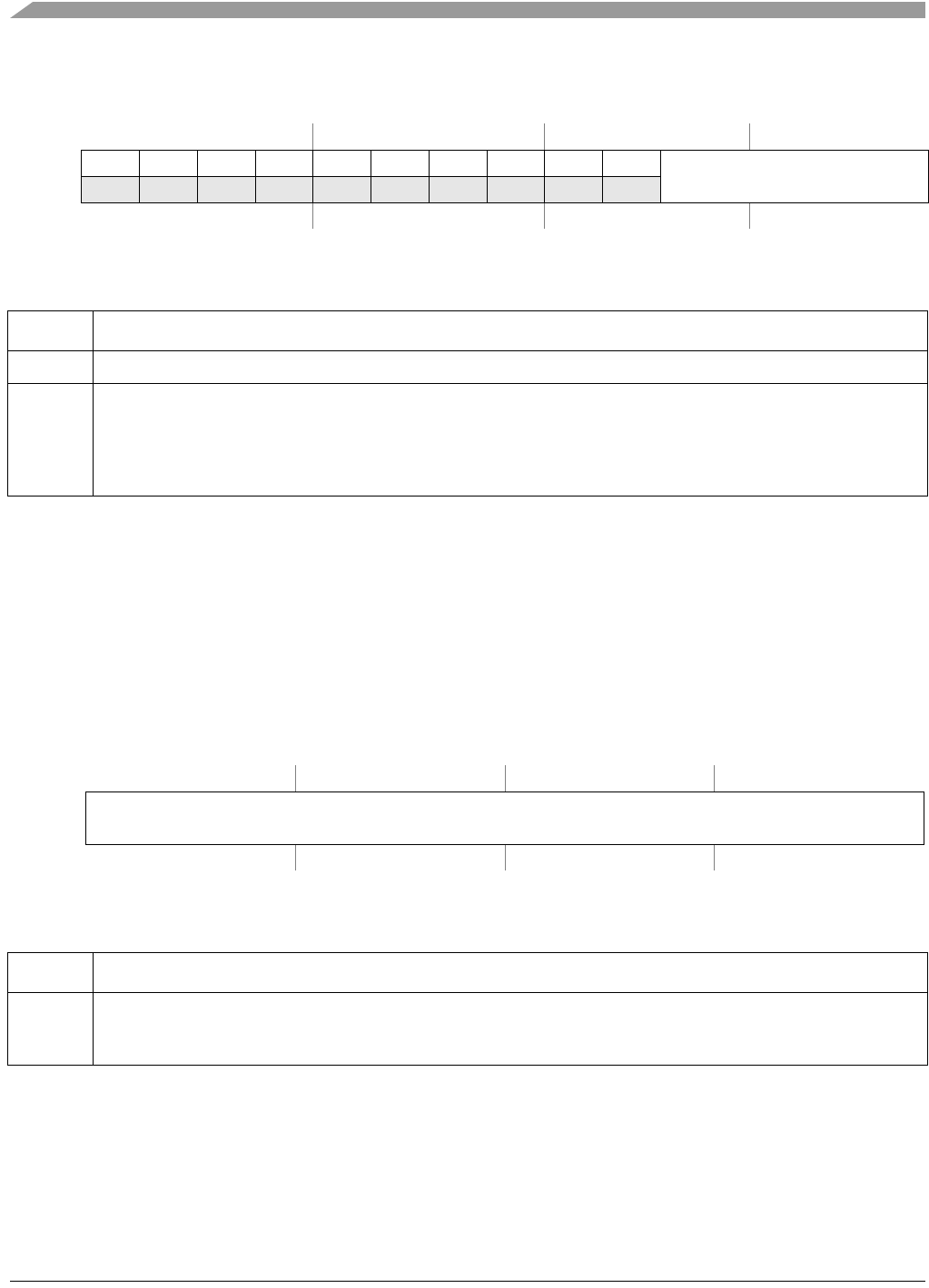

IPSBAR

Offset:

0x00_0354 (QDR) Access: User read/write

1514131211109876543210

R

DATA

W

Reset0000000000000000

Figure 23-8. QSPI Data Register (QDR)

Table 23-8. QDR Field Descriptions

Field Description

15–0

DATA

A write to this field causes data to be written to the QSPI RAM entry specified by QAR[ADDR]. Similarly, aread of

this field returns the data in the QSPI RAM at the address specified by QAR[ADDR]. During command RAM

accesses (QAR[ADDR] = 0x20–0x2F), only the most significant byte of this field is used.