Debug Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

28-46 Freescale Semiconductor

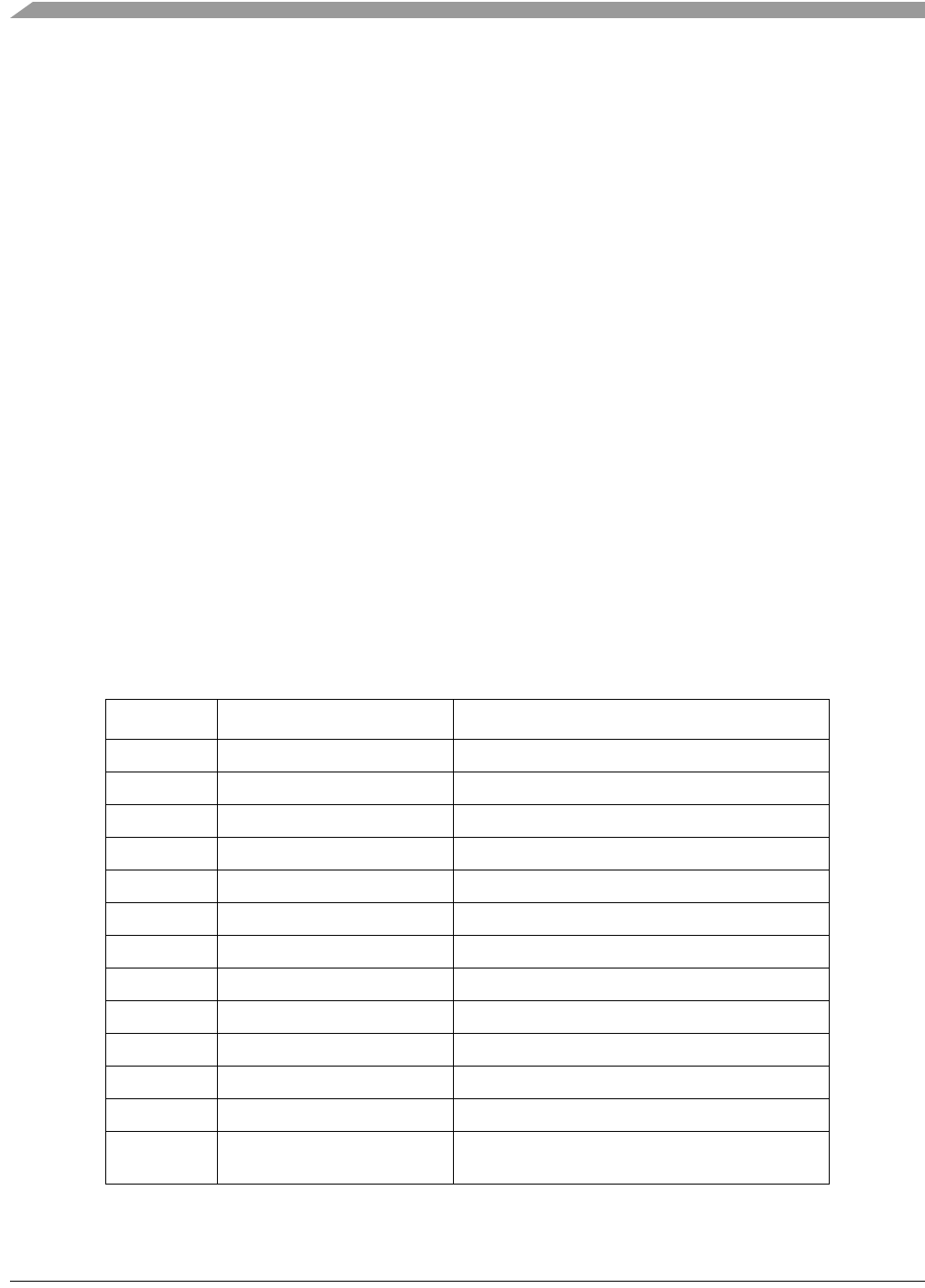

Table 28-26 shows the PST/DDATA specification for multiply-accumulate instructions.

1

During normal exception processing, the PST output is driven to a 0xC indicating the exception processing state.

The exception stack write operands, as well as the vector read and target address of the exception handler may also

be displayed.

Exception Processing:

PST = 0xC,

{PST = 0xB,DD = destination}, // stack frame

{PST = 0xB,DD = destination}, // stack frame

{PST = 0xB,DD = source}, // vector read

PST = 0x5,{PST = [0x9AB],DD = target}// handler PC

The PST

/DDATA specification for the reset exception is shown below:

Exception Processing:

PST = 0xC,

PST = 0x5,{PST = [0x9AB],DD = target}// handler PC

The initial references at address 0 and 4 are never captured nor displayed because these accesses are treated as

instruction fetches.

For all types of exception processing, the PST = 0xC value is driven at all times, unless the PST output is needed

for one of the optional marker values or for the taken branch indicator (0x5).

2

For JMP and JSR instructions, the optional target instruction address is displayed only for those effective address

fields defining variant addressing modes. This includes the following <ea>x values: (An), (d16,An), (d8,An,Xi),

(d8,PC,Xi).

3

For move multiple instructions (MOVEM), the processor automatically generates line-sized transfers if the operand

address reaches a 0-modulo-16 boundary and there are four or more registers to be transferred. For these line-sized

transfers, the operand data is never captured nor displayed, regardless of the CSR value.

The automatic line-sized burst transfers are provided to maximize performance during these sequential memory

access operations.

Table 28-26. PST/DDATA Values for User-Mode Multiply-Accumulate Instructions

Instruction Operand Syntax PST/DDATA

mac.l Ry,Rx PST = 0x1

mac.l Ry,Rx,<ea>y,Rw, PST = 0x1, {PST = 0xB, DD = source operand}

mac.w Ry,Rx PST = 0x1

mac.w Ry,Rx,ea,Rw PST = 0x1, {PST = 0xB, DD = source operand}

move.l {Ry,#<data>},ACC PST = 0x1

move.l {Ry,#<data>},MACSR PST = 0x1

move.l {Ry,#<data>},MASK PST = 0x1

move.l ACC,Rx PST = 0x1

move.l MACSR,CCR PST = 0x1

move.l MACSR,Rx PST = 0x1

move.l MASK,Rx PST = 0x1

msac.l Ry,Rx PST = 0x1

msac.l Ry,Rx,<ea>y,Rw PST = 0x1, {PST = 0xB, DD = source},

{PST = 0xB, DD = destination}