8051

Architectural Specification and Functional Description

COUNTERI

INTERRUPT

GATE

TIMER

REQUEST

TIMERI

RUN

•

COUNTER

~

OIN

-

MODE 3

G

J

)-

Hn

PULSE

TO

SERIAL

PORT

COUNTER 1

MODE

0:

8-BIT TIMER WITH PRESCALERI

8-BIT COUNTER WITH PRESCALER-

MODE

1: 16-BIT TIMER/COUNTER

MODE 2: 8-BIT AUTO-RELOAD TIC

MODE

3:

PREVENTS INCREMENTING

OF TIC 1

J

>-

--

1"'"

~

r-r-

INT1

:=fJ-

T1

~r~

-r-

-

-

1

"'

COUNTER 0

XTAL1

+12

~

-

~

8-8ITTIMER

~

(THO)

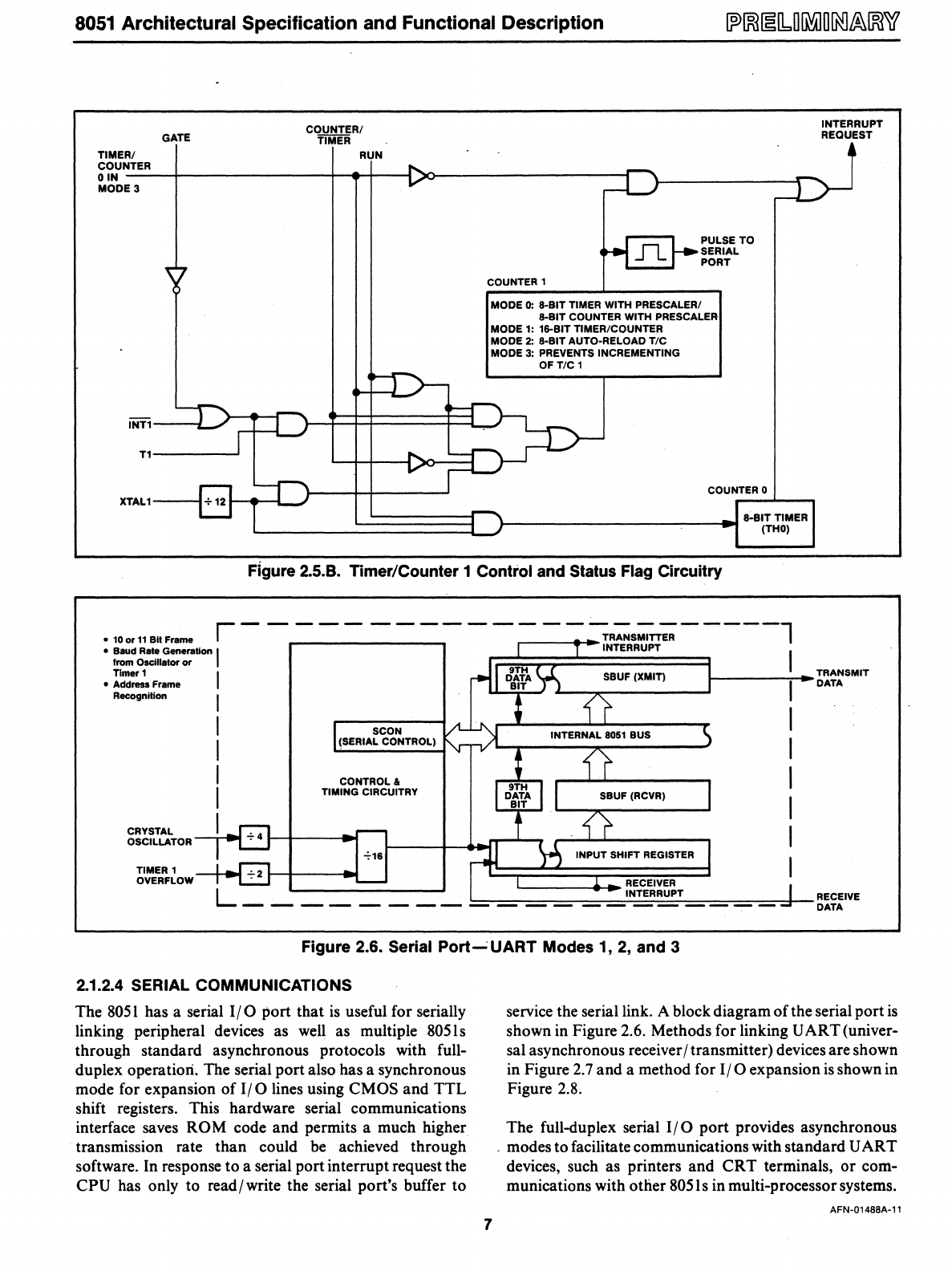

Figure 2.5.8. Timer/Counter 1 Control and Status Flag Circuitry

• 100r11

Bit

Frame r - - -

--

- -

--

-

--

-

---:;:R:;:;S;.-TT-;;-----l

• Baud

Rate

Generetlon I INTERRUPT

from Oscillator

or

Timer 1 I

• Address Frame

Recognition I

I

I

I

I

g:~~~~t.,.OR

-

....

1 .....

TIMER 1

SCON

(SERIAL CONTROL)

CONTROL"

TIMING CIRCUITRY

-:-16

I-

___

-:-

__

~~~~SMIT

~-~-----~

OVERFLOW

RECEIVER

L

______________

~~

___

_

RECEIVE

DATA

Figure 2.6. Serial

Port~UART

Modes 1, 2, and 3

2.1.2.4 SERIAL COMMUNICATIONS

The

8051

has a serial

I/O

port that

is

useful for serially

linking peripheral devices as

well

as

multiple805ls

through standard asynchronous protocols with full-

duplex operatiori. The serial port also has a synchronous

mode for expansion of

I/O

lines using CMOS and TTL

shift registers. This hardware serial communications

interface saves

ROM code and permits a much higher

transmission rate than could be achieved through

software. In response

to

a serial port interrupt request the

CPU has only to read/write the serial port's buffer to

7

service the serial link. A block diagram

of

the serial port

is

shown in Figure 2.6. Methods for linking U

ART

(univer-

sal asynchronous receiver / transmitter) devices are shown

in Figure

2.7

and a method for

I/O

expansion

is

shown in

Figure 2.8.

The full-duplex serial

I/O

port provides asynchronous

o modes to facilitate communications with standard U

ART

devices, such as printers and

CRT

terminals, or com-

munications with other

8051s in multi-processor systems.

AFN-01488A-11