8051

Architectural Specification and Functional Description

SYMBOLIC

BYTE

ADDRESS

BIT

ADDRESS

ADDRESS

~(

A.

\~

'F

2481

B

~I:

(FOH)

A

(EOH)

ACC

231

psw

I

224 I 208

(DOH)

IPC 1

215

208 I 184

(B8H)

P3

I

191

184

1

(BOH)

176

1

183

176 I 168

(ASH)

IEC

P2 I 175

168

160 I 160

(AOH)

SFR's

167

CONTAINING

SBUF I

1

153

(99H)

DIRECT

(98H)

ADDRESSABLE

SCON

BITS

152

P1

I 159 152 I 144

(9OH)

151

144

TH1

141

(8DH)

THO

140 (8CH)

Tl1

139 (8BH)

TlO

138 (BAH)

TMOD

137

(89H)

TCON

136 (88H)

:~

~143 136

~:

::::

SP 129 (81H)

PO 128 (SOH)

135 128

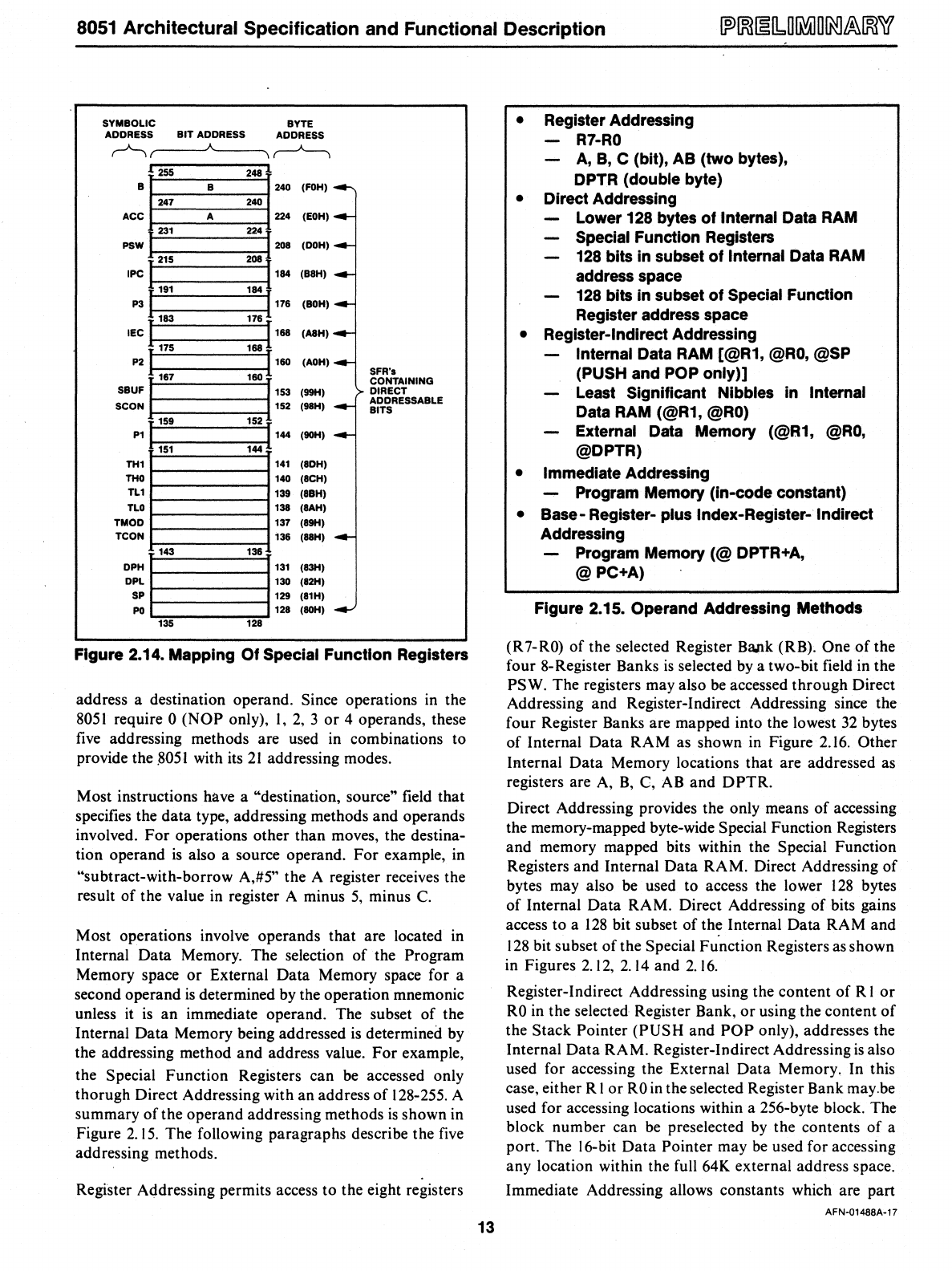

Figure 2.14. Mapping Of Special Function Registers

address a destination operand.

Since operations in the

8051

require 0

(NOP

only), I,

2,

3

or

4 operands, these

five addressing methods are used in combinations to

provide the

.8051

with its

21

addressing modes.

Most instructions have a

"destination, source'" field that

specifies the

data

type, addressing methods and operands

involved.

For

operations other than moves, the destina-

tion operand

is

also a source operand.

For

example, in

"subtract-with-borrow

A,#5" the A register receives the

result

of

the value in register A minus

5,

minus

C.

Most operations involve operands that are located in

Internal Data Memory. The selection of the Program

Memory space

or

External Data Memory space for a

second operand

is

determined by the operation mnemonic

unless it

is

an immediate operand. The subset

of

the

Internal

Data

Memory being addressed

is

determined by

the addressing method and address value.

For

example,

the

Special Function Registers can be accessed only

thorugh Direct Addressing with an address

of

128-255. A

summary

of

the operand addressing methods

is

shown in

Figure 2.15. The following paragraphs describe the five

addressing methods.

Register Addressing permits access to the eight registers

13

• Register Addressing

R7-RO

--

A,

B,

C (bit), AB (two bytes),

DPTR (double byte)

• Direct Addressing

Lower 128 bytes

of

Internal Data RAM

Special Function Registers

128

bits in subset

of

Internal Data RAM

address space

128

bits in subset

of

Special Function

Register address space

• Register-Indirect Addressing

Internal Data RAM [@R1,

@RO,

@SP

(PUSH and POP only))

Least Significant Nibbles in Internal

Data RAM (@R1,

@RO)

External Data Memory

(@R1,

@RO,

@DPTR)

• Immediate Addressing

--

Program Memory (tn-code constant)

• Base - Register- plus Index-Register- Indirect

Addressing

Program Memory

(@

DPTR+A,

@PC+A)

Figure 2.15. Operand Addressing Methods

(R

7-RO)

of the selected Register Bank (RB). One

of

the

four 8-Register Banks

is

selected

by

a two-bit field in the

PSW. The registers may also be accessed

through

Direct

Addressing and Register-Indirect Addressing since the

four Register Banks are mapped into the lowest

32

bytes

of Internal

Data

RAM

as shown in Figure

2.16.

Other

Iflternal

Data

Memory locations that are addressed as

registers are

A,

B,

C,

AB

and

DPTR.

Direct Addressing provides the only means

of

accessing

the memory-mapped byte-wide

Special Function Registers

and memory mapped bits within the

Special Function

Registers and Internal

Data

RAM. Direct Addressing

of

bytes may also be used to access the lower

128

bytes

of Internal

Data

RAM. Direct Addressing

of

bits gains

access to a

128

bit subset of the Internal Data RAM and

128

bit subset

of

the Special Function Registers as shown

in Figures

2.

12,

2.

14

and

2.

16.

Register-Indirect Addressing using the content

of

R I

or

RO

in the selected Register Bank,

or

using the content

of

the Stack Pointer

(PUSH

and

POP

only), addresses the

Internal

Data

RAM. Register-Indirect Addressing

is

also

used for accessing the External

Data

Memory. In this

case, either R 1

or

RO

in

the selected Register Bank may.be

used for accessing locations within a 256-byte block. The

block number can be preselected

by

the contents

of

a

port. The 16-bit

Data

Pointer may

be

used for accessing

any location within the full 64K external address space.

Immediate Addressing allows constants which are part

AFN'01488A-17