8051

Architectural Specification and Functional Description

of the instruction to be accessed from the Program

Memory.

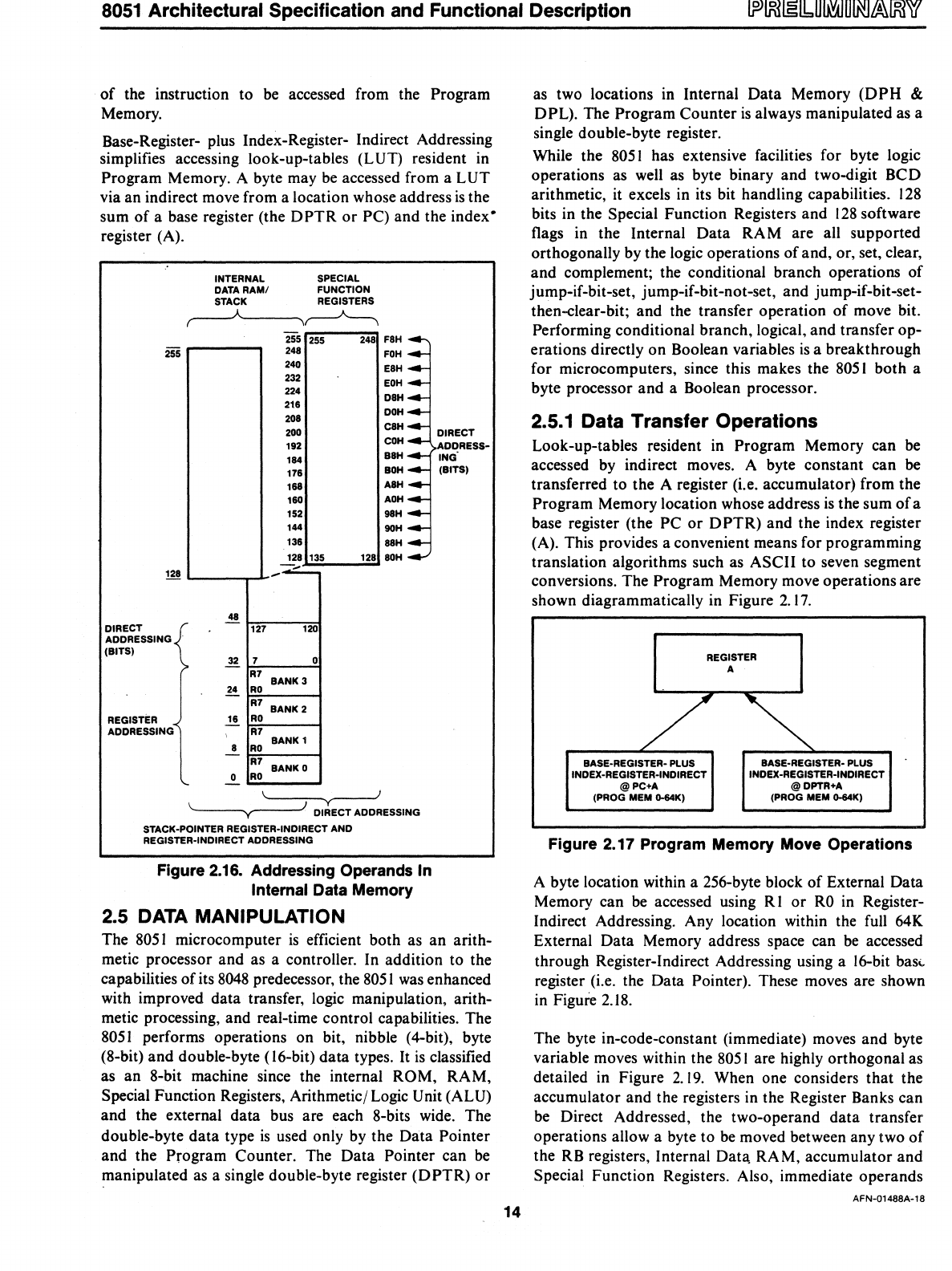

Base-Register- plus Index-Register- Indirect Addressing

simplifies accessing look-up-tables

(LUT) resident in

Program Memory. A byte may

be

accessed from a LUT

via an indirect move from a location whose address

is

the

sum

of

a base register (the

DPTR

or PC) and the index·

register (A).

DIRECT

ADDRESSING

(BITS)

REGISTER

ADDRESSING

INTERNAL

DATA

RAMI

STACK

SPECIAL

FUNCTION

REGISTERS

~~

255 255

248

248

240

232

224

216

208

200

192

164

176

168

160

152

144

136

128 135 128

..,.....:::.-

~

127

120

.E.

7 0

R7

BANK 3

24

RO

R7

BANK2

.!!

RO

,

R7

BANK

1

8

RO

R7

BANKO

'-

0

RO

F8H

FOH

E8H

EOH

D8H

DOH

C8H

COH

B8H

BOH

ASH

AOH

98H

90H

88H

80H

~

"~--~y

) DIRECT ADDRESSING

STACK-POINTER REGISTER-INDIRECT

AND

REGISTER-INDIRECT ADDRESSING

Figure

2.16.

Addressing Operands In

Internal Data Memory

2.5

DATA MANIPULATION

DIRECT

ADDRESS-

ING

(BITS)

The

8051

microcomputer

is

efficient both as an arith-

metic processor and as a controller. In addition to the

capabilities of its

8048

predecessor, the

8051

was

enhanced

with improved data transfer, logic manipulation,

arith-

metic processing, and real-time control capabilities. The

8051

performs operations on bit, nibble (4-bit), byte

(8-bit) and double-byte (l6-bit) data types.

It

is

classified

as an 8-bit machine since the internal

ROM, RAM,

Special Function Registers, Arithmetic/ Logic

Unit (ALU)

and the external data bus are each 8-bits wide. The

double-byte data type

is

used only

by

the Data Pointer

and the

Program Counter. The

Data

Pointer can

be

manipulated

as

a single double-byte register (DPTR)

or

14

as two locations

in

Internal Data Memory

(DPH

&

DPL). The Program Counter

is

always manipulated as a

single double-byte register.

While the

8051

has extensive facilities for byte logic

operations as well as byte binary and two-digit BCD

arithmetic, it excels in its bit handling capabilities.

128

bits in the Special Function Registers and

128

software

flags in the Internal Data RAM are all supported

orthogonally

by

the logic operations of and, or, set, clear,

and complement; the conditional branch operations

of

jump-if-bit-set, jump-if-bit-not-set, and jump-if-bit-set-

then-clear-bit; and the transfer operation

of

move bit.

Performing conditional branch, logical, and transfer

op-

erations directly on Boolean variables

is

a breakthrough

for microcomputers, since this makes the

8051

both a

byte processor and a Boolean processor.

2.5.1 Data Transfer Operations

Look-up-tables resident

in

Program Memory can be

accessed

by

indirect moves. A byte constant can be

transferred to the A register

(Le.

accumulator) from the

Program Memory location whose address

is

the sum

of

a

base register (the PC

or

DPTR)

and the index register

(A). This provides a convenient means for programming

translation algorithms such as

ASCII to seven segment

conversions. The Program Memory move operations are

shown diagrammatically in Figure

2.

17.

BASE-REGISTER- PLUS

INDEX-REGISTER-INDIRECT

@PC+A

(PROG MEM 0-64K)

REGISTER

A

BASE-REGISTER- PLUS

INDEX-REGISTER-INDIRECT

@OPTR+A

(PROG MEM 0-64K)

Figure 2.17 Program

Memory

Move Operations

A byte location within a 256-byte block of External Data

Memory can

be

accessed using R I or

RO

in

Register-

Indirect Addressing. Any location within the full 64K

External Data Memory address space can

be

accessed

through Register-Indirect Addressing using a 16-bit bas

..

register (i.e. the Data Pointer). These moves are shown

in Figure

2.18.

The byte in-code-constant (immediate) moves and byte

variable moves within the

8051

are highly orthogonal as

detailed

in

Figure

2.

19.

When one considers that the

accumulator and the registers in the Register Banks can

be

Direct Addressed, the two-operand data transfer

operations allow a byte to

be

moved between any two

of

the

RB

registers, Internal Data, RAM, accumulator and

Special Function Registers. Also, immediate operands

AFN-01488A-18