8051 Architectural Specification and Functional Description

There are three arithmetic operations that operate

exclusively on the

A· register. These are the decimal-

adjust for BCD addition and the two test conditions

shown in Figure 2.25. The decimal-adjust operation

converts the result from a binary addition

of

two two-digit

BCD values to yield the correct two-digit BCD result.

During this operation the auxiliary-carry flag helps effect

the proper adjustment. Conditional branches may be

taken based on the value in the A register being zero

or

not zero.

• Jump-lf-A-ls.Zero

REG~TER

• Declmal-Add-Adjust

[:EJ

• Jump-I'·A-Is-Nol·Zero

Figure 2.25. Internal Data Memory Arithmetic

Operations (Register A Specific)

The

805

I simplifies the implementation

of

software

counters since the increment and decrement operations

can be performed on the A register, a register in the

selected Register Bank,

an

Indirect Addressed byte in the

Internal Data RAM

or

a byte in the Direct Addressed

Internal Data RAM or Special Function Register. The

16-bit

Data

Pointer can

be

incremented.

For

efficient

loop control the decrement-and-jump-if-not-zero opera-

tion

is

provided. This operation can test a register in the

selected Register Bank, any Special Function Register

or

any byte

of

Internal Data RAM accessible through Direct

Addressing and force a branch if it

is

not zero. The incre-

ment

I decrement operations are summarized in Figure

2.26.

• Increment (INC)

• Decremeilt

(DEC)

• Decremenl-And.Jump-tf-Nol-Zero

(DJNZ)

DIRECT

Dala

(INC,

DEC, DJNZ)

REGISTER

R7-RO

(INC, DEC, DJNZ)

REGISTER

A

(INC, DEC)

REGISTER

.

DPTR

(INC)

REGISTER-INDIRECT

@R1,@RO

(INC, DEC)

Figure 2.26. Internal Data Memory Arithmetic

Operations

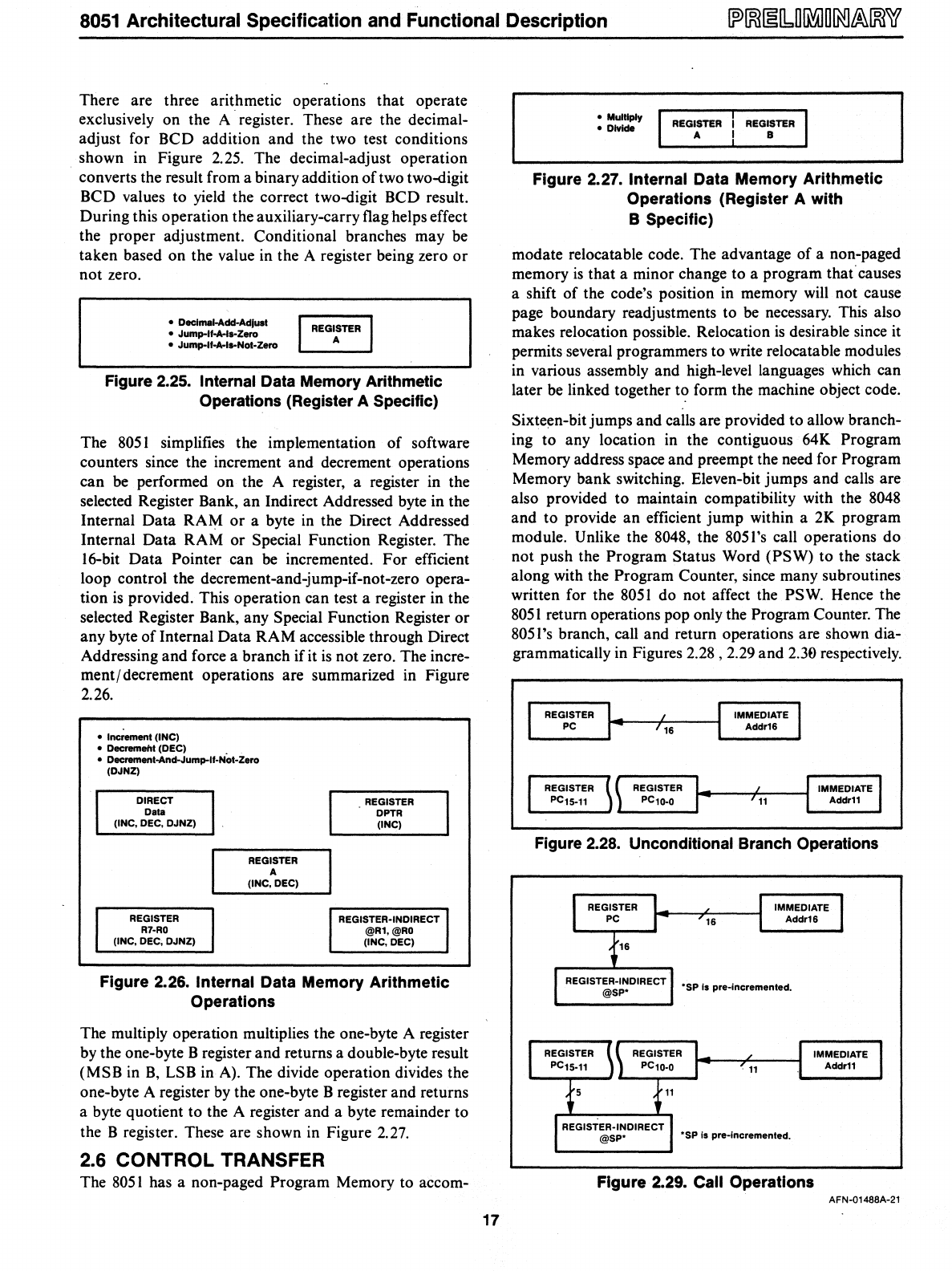

The mUltiply operation multiplies the one-byte A register

by the one-byte B register and returns a double-byte result

(MSB in

B,

LSB in

A).

The divide operation divides the

one-byte A register by the one-byte B register and returns

a byte quotient to the A register and a byte remainder to

the B register. These are shown in Figure 2.27.

2.6

CONTROL TRANSFER

The

805

I has a non-paged Program Memory to accom-

17

::':

r

REGISTERT

REGISTER 1

A I B

Figure 2.27. Internal Data Memory Arithmetic

Operations (Register A with

B Specific)

modate relocatable code. The advantage

of

a non-paged

memory

is

that a minor change to a program

tha(

causes

a shift

of

the code's position in memory will not cause

page boundary readjustments to

be

necessary. This also

makes relocation possible. Relocation

is

desirable since it

permits several programmers to write relocatable modules

in various assembly and high-level languages which can

later

be

linked together to form the machine object code.

Sixteen-bit jumps and calls are provided to allow branch-

ing to any location in the contiguous 64K Program

Memory address space and preempt the need for Program

Memory bank switching. Eleven-bit jumps and calls are

also provided to maintain compatibility with the

8048

and to provide

an

efficient

jump

within a 2K program

module.

Unlike the 8048, the 8051's call operations do

not push the Program

Status Word (PSW) to the stack

along with the Program Counter, since many subroutines

written for the

8051

do not affect the PSW. Hence the

8051

return operations pop only the Program Counter. The

8051

's branch, call and return operations are shown dia-

grammatically in Figures 2.28 , 2.29 and

2.3f>

respectively.

REGplSCTER

1"'"4e-_-I-(~_--I~I_MM_E_D_'A_:r_E

,.j

_

/16

_ Addr16

11

Figure 2.28. Unconditional Branch Operations

16

·SP

is pre-incremented.

.

11

*SP

is

pre

..

incremented.

Figure 2.29. Call Operations

AFN-Ol488A-21