8051

Architectural Speciffcation ancrFunctionaJ Descrlpfion

t

64K

64K

EXTERNAl-

OYERl-APPED SPACE

I

------

-"Lr-----A

4095

'l

INTERNAl-

255 I I

25S

,

I I

1~1..

I

128

,

-

PROGRAM

COUNTER

0

,

,

PROGRAM

MEMORY

J

,

INTERNAl-

DATA RAM

,

-

,

SPECIAL

FUNCTION

REGISTERS

INTERNAL

DATA MEMORY

,

,

EXTERNAL

DATA

MEMORY

,

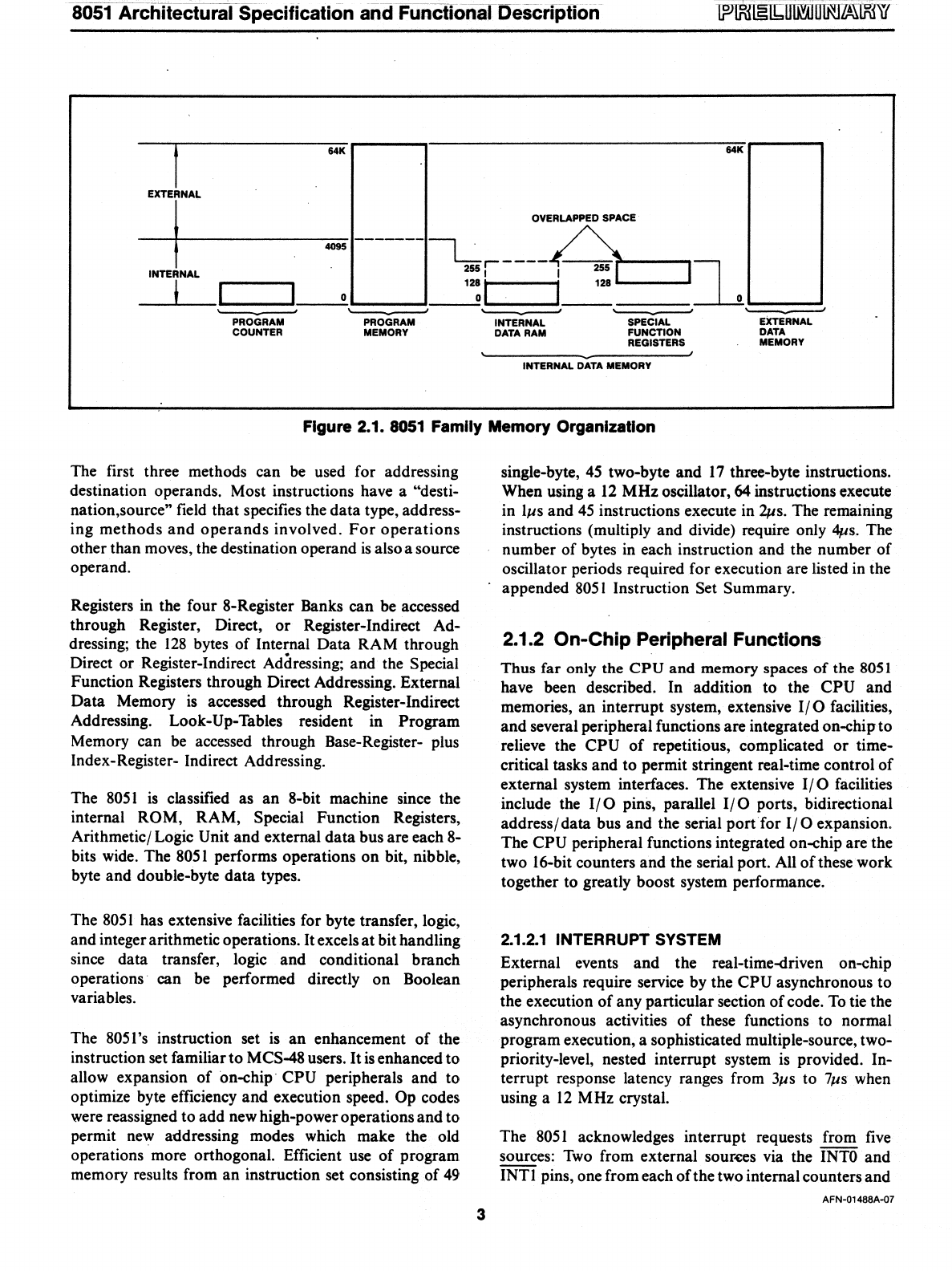

Figure 2.1.

8051

Family Memory Organization

The first three methods can

be

used for addressing

destination operands. Most instructions have a

"desti-

nation,source" field that specifies the data type, address-

ing methods

and

operands

involved.

For

operations

other than moves, the destination operand

is

also a source

operand.

Registers

in the four 8-Register Banks can

be

accessed

through Register, Direct,

or

Register-Indirect Ad-

dressing; the

128

bytes of Internal Data RAM through

Direct or Register-Indirect Addressing; and the

Special

Function Registers through Direct Addressing. External

Data Memory

is

accessed through Register-Indirect

Addressing. Look-Up-Tables resident in Program

Memory can

be

accessed through Base-Register- plus

Index-Register- Indirect Addressing.

The

80S

1

is

classified as an 8-bit machine since the

internal

ROM, RAM, Special Function Registers,

Arithmeticl

Logic Unit and external data bus are each

8-

bits wide. The

80S

1 performs operations on bit, nibble,

byte and double-byte data types.

The

80S1

has extensive facilities for byte transfer, logic,

and integer arithmetic operations. It excels

at

bit handling

since data transfer, logic and conditional branch

operations· can be performed directly on Boolean

variables.

The

80S

I's instruction set

is

an

enhancement

of

the

instruction set familiar to

MCS-48 users.

It

is

enhanced to

allow expansion of

on-chip· CPU peripherals and to

optimize byte efficiency and execution speed.

Op codes

were reassigned to add new high-power operations and to

permit

new

addressing modes which make the old

operations more orthogonal. Efficient use

of

program

memory results from an instruction set consisting of

49

3

single-byte,

4S

two-byte and

17

three-byte instructions.

When using a

12

MHz oscillator, 64 instructions execute

in

IlJs

and

4S

instructions execute in

4ls.

The remaining

instructions (multiply and divide) require only

~s.

The

number of bytes

in

each instruction and the number

of

oscillator periods required for execution are listed in the

appended

80S

I Instruction Set Summary.

2.1.2 On-Chip Peripheral Functions

Thus

far

only

the

CPU

and

memory

spaces

of

the

80S 1

have been described. In addition to the CPU and

memories, an interrupt system, extensive

I/O

facilities,

and several peripheral functions are integrated on-chipto

relieve the CPU

of

repetitious, complicated

or

time-

critical tasks and to permit stringent real-time control

of

external system interfaces. The extensive 110 facilities

include the

110 pins, parallel 110 ports, bidirectional

address/data bus and the serial port for

I/O

expansion.

The CPU peripheral functions integrated on-chip are the

two 16-bit counters and the serial port. All

of

these work

together to greatly boost system performance.

2.1.2.1

INTERRUPT SYSTEM

External events and the

real~time-driven

on-chip

peripherals require service by the CPU asynchronous to

the execution

of

any particular section

of

code.

To

tie the

asynchronous activities of these functions to normal

program execution, a sophisticated multiple-source,

two~

priority-level, nested interrupt system

is

provided. In-

terrupt response latency ranges from

3IJs

to

7IJs

when

using a

12

MHz crystal.

The

80S

I acknowledges interrupt requests from

five

sources:

Two

from external sour.res

via

the

INTO

and

INTI pins, one from each

of

the two internal counters and

AFN-Ol488A-D7