124

CHAPTER 5 CPU ARCHITECTURE

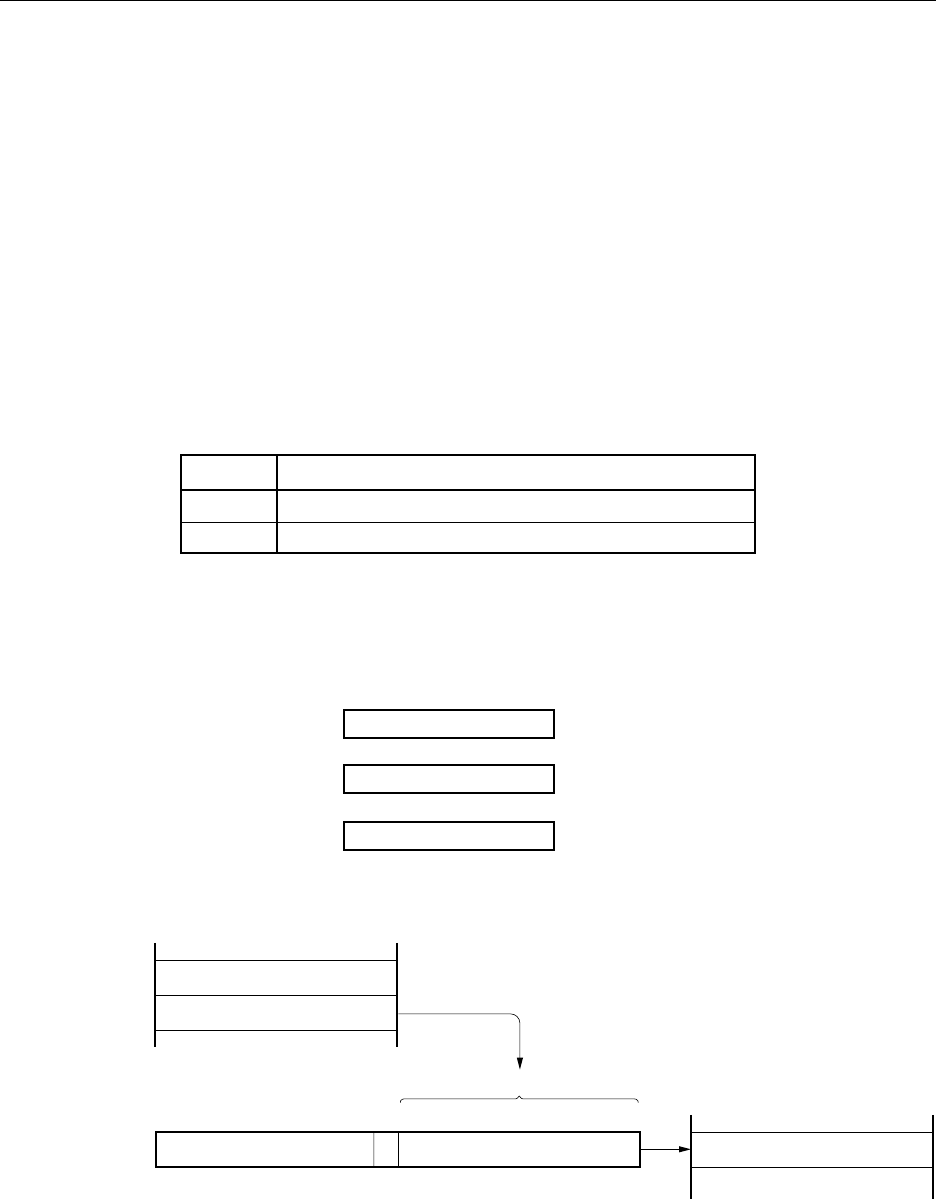

5.4.4 Short direct addressing

[Function]

The memory to be manipulated in the fixed space is directly addressed with 8-bit data in an instruction word.

The fixed space to which this address is applied is a 256-byte space of addresses FE20H through FF1FH. An

internal high-speed RAM and a special-function register (SFR) are mapped at FE20H to FEFFH and FF00H to

FF1FH, respectively.

The SFR area (FF00H through FF1FH) to which short direct addressing is applied is a part of the entire SFR

area. To this area, ports frequently accessed by the program, and the compare registers and capture registers

of timer/event counters are mapped. These SFRs can be manipulated with a short byte length and a few clocks.

When 8-bit immediate data is at 20H to FFH, bit 8 of an effective address is set to 0. When it is at 00H to 1FH,

bit 8 is set to 1. Refer to [Illustration] on next page.

[Operand format]

Identifier Description

saddr Label of FE20H to FF1FH immediate data

saddrp Label of FE20H to FF1FH immediate data (even address only)

15

0

Short Direct Memory

Effective Address

1

111111

87

07

OP code

saddr-offset

α

[Description example]

MOV 0FE30H, #50H; when setting saddr to FE30H and immediate data to 50H

Operation code 0 0 0 10001 OP code

00110000 30H (saddr-offset)

01010000 50H (immediate data)

[Illustration]

When 8-bit immediate data is 20H to FFH, α = 0

When 8-bit immediate data is 00H to 1FH, α = 1