196

CHAPTER 8 16-BIT TIMER/EVENT COUNTER

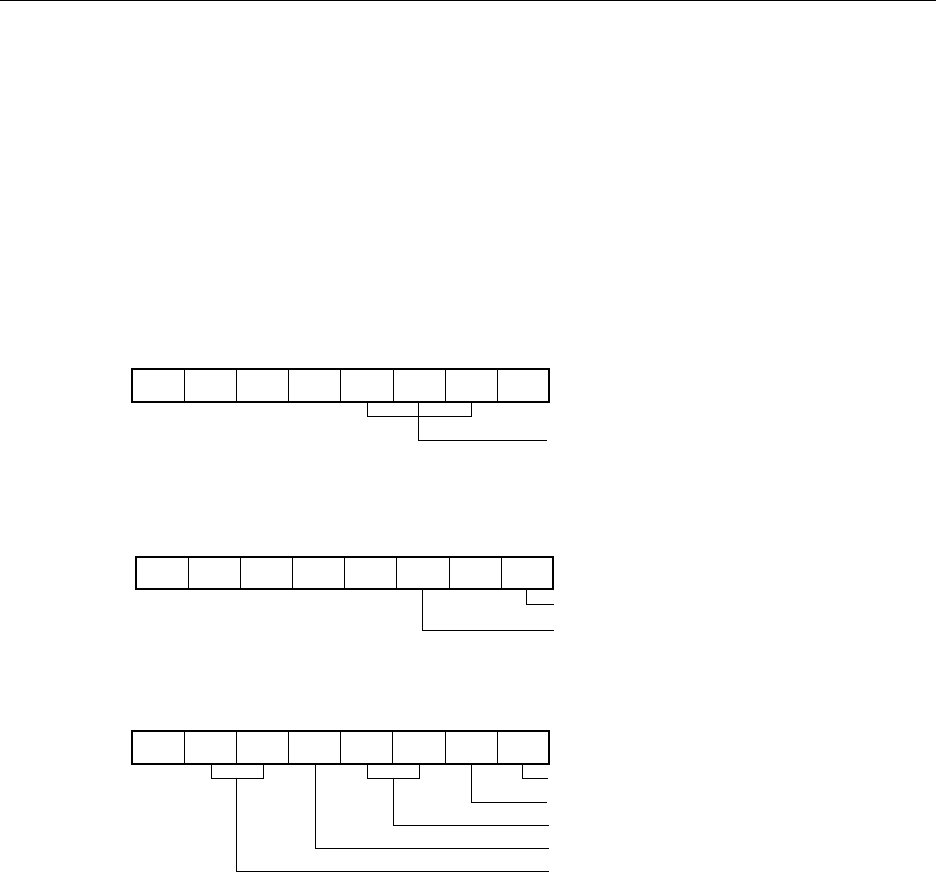

TOC0 110/10/11000

TOE0

TOC01LVR0LVS0

Inversion of output on match of TM0 and CR00

TOC04OSPEOSPT

TO0 Output Enabled

Specified TO0 output F/F initial value

Inversion of output on match of TM0 and CR01

One-shot pulse output disabled

CRC0 0x000000

CRC00CRC01CRC02

CR00 set as compare register

CR01 set as compare register

TMC0 00110000

OVF0

TMC01TMC02TMC03

Clear & start on match of TM0 and CR00

8.5.3 PPG output operations

Setting the 16-bit timer mode control register (TMC0) and capture/compare control register 0 (CRC0) as shown

in Figure 8-16 allows operation as PPG (Programmable Pulse Generator) output.

In the PPG output operation, square waves are output from the TO0/P30 pin with the pulse width and the cycle

that correspond to the count values set beforehand in 16-bit capture/compare register 01 (CR01) and in 16-bit capture/

compare register 00 (CR00), respectively.

Figure 8-16. Control Register Settings for PPG Output Operation

(a) 16-bit timer mode control register (TMC0)

(b) Capture/compare control register 0 (CRC0)

(c) 16-bit timer output control register (TOC0)

Caution Values in the following range should be set in CR00 and CR01:

0000H ≤ CR01 < CR00 ≤ FFFFH

Remark × : Don't care