1.2.2 Hardware Break

This function causes the target program to stop upon detecting a data read/write to memory,

instruction execution, or the rising/falling edge of the input signal fed from an external trace cable.

The contents of events that can be set vary with each target MCU.

The following designations are available as break events:

• Address designation

- Instruction fetch

- Memory access

- Bit access

• External trigger designation

• Interruption

The number of events that can be specified are six events of all. For the address designation method,

instruction fetch and memory access allow the range designation and logical condition designation, in

addition to the normal one-address designation. Moreover, instruction fetch allows you to specify the

function name.

Memory access allows you to specify the comparison data to read/write data related to the specified

address in the same manner as when setting the H/W breakpoint. It also allows mask designation to

the comparison data.

These break events can be combined as below:

• Trace when all of the valid events are established (AND condition)

• Trace when all of the valid events are established at the same time (simultaneous AND condition)

• Trace when one of the valid events is established (OR condition)

• Trace upon entering a break state during state transition (State Transition condition)

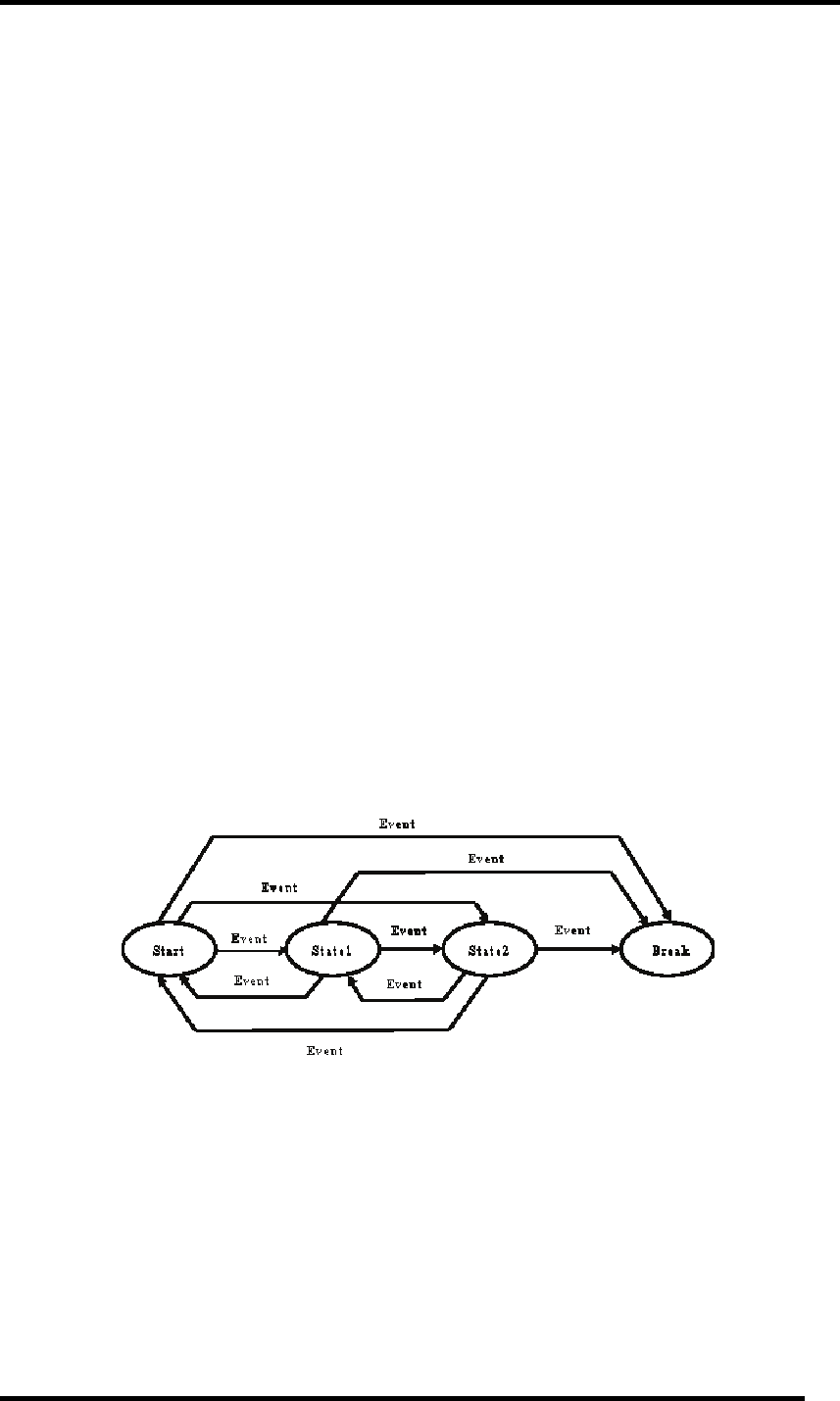

When transitional conditions set in an interstate pass are met, a state transition occurs, in which case

the target program can be made to stop upon entering a break state. The conceptual diagram shown

below depicts the relationship between state and pass.

State transition break allows you to select "specified task only" (or "other than specified task") as the

break condition to meet the real time OS.

4