7.11.7 Display of bus information on the M16C/R8C Debugger

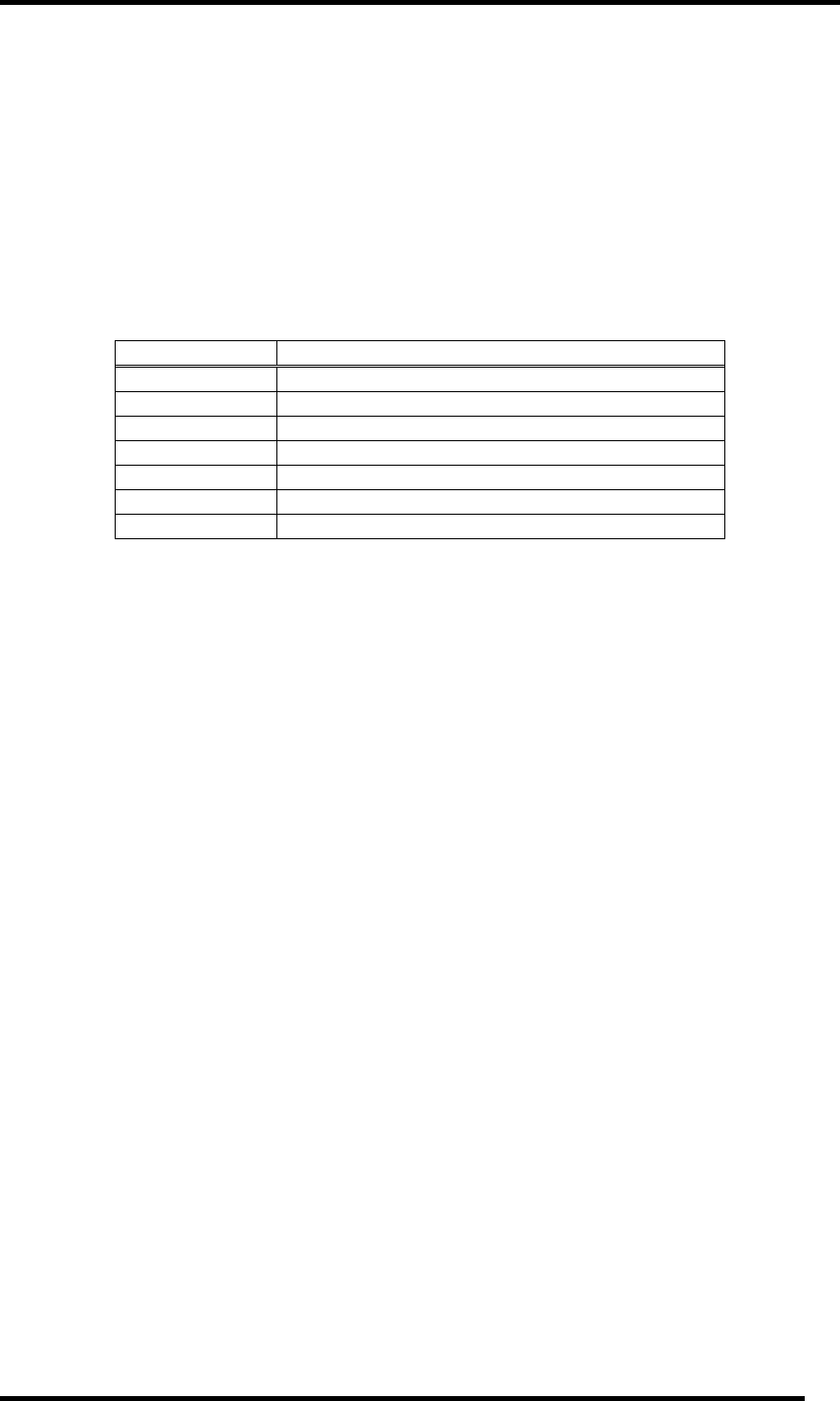

From left to right, the contents are as follows:

• Address

The status of the address bus

• Data

The status of the data bus

• BUS

The width of the external data bus ("8b" for an 8-bit data bus, and "16b" for a 16-bit data bus)

• BIU

This shows the status between the BIU (bus interface unit) and memory, and BIU and I/O.

Display format

Status

- No change

DM A Data access other than a C U cause such as DMA P

IN T Start of INTACK sequence

IB Instruction code read due to CPU cau e (bytes) s

DB Data access due to CPU cause (bytes)

IW Instruction code read due to CPU caus (words) e

DW Data access due to CPU cause (words)

• R/W

Shows the status of the data bus ("R" for read, "W" for write, "-" for no access).

• RWT

This signal shows the effective position in the bus cycle ("0" when effective. Address, Data, and

BIU signals are valid when RWT is "0".

• CPU

Shows the status between CPU and BIU (bus interface unit )

178