Chapter 3 Hardware

34 Reference Manual XTX 820

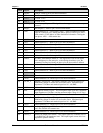

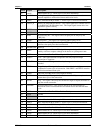

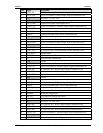

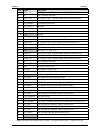

Pin # Signal Description

59 PCIE1_TX- PCI Express Lane 1, Transmit Output, Negative Differential Line

60 NC Not Connected (Reserved )

61 PCIE1_TX+ PCI Express Lane 1, Transmit Output, Positive Differential Line

62 NC Not Connected (Reserved )

63 PCE_WAKE* PCI Express Wake Event

64 PCI_GNT#A Reserved

65 NC Not Connected (Reserved )

66 PCI_REQ#A Reserved

67, 68 GND Ground

69 PCIE0_RX- PCI Express Lane 0, Receive Input, Negative Differential Line

70 NC Not Connected (Reserved )

71 PCIE0_RX+ PCI Express Lane 0, Receive Input, Positive Differential Line

72 NC Not Connected (Reserved )

73 GND Ground

74 VCC DC Power – +5 VDC, ±5%

75 PCIE0_TX- PCI Express Lane 0, Transmit Output, Negative Differential Line

76 NC Not Connected (Reserved )

77 PCIE0_TX+ PCI Express Lane 0, Transmit Output, Positive Differential Line

78 NC Not Connected (Reserved )

79 CODECSET AC`97/HDA Disable onboard Audio CODEC

80 VCC DC Power +5VDC, ±5%

81 AC_RST* AC'97/HDA CODEC Reset

82 AC_SDOUT AC'97/HDA Audio Serial Data Output to CODEC

83, 84 VCC DC Power – +5 VDC, ±5%

85 AC_SYNC AC'97/HDA Serial Bus Synchronization

86 AC_SDIN0 AC'97/HDA Audio Serial Data Input from CODEC0

87 AC_SDIN1 AC'97/HDA Audio Serial Data Input from CODEC1

88 AC_SDIN2 AC'97/HDA Audio Serial Data Input from CODEC2

89 AC_BIT_CLK AC'97/HDA 12.228 MHz Serial Bit Clock from CODEC

90 FAN_TACHOIN Fan tachometer input

91 LPC_AD0 LPC Multiplexed Command, Address and Data line 0

92 FAN_PWMOUT Fan speed control

93 LPC_AD1 LPC Multiplexed Command, Address and Data line 1

94 LPC_FRAME* LPC Frame – Indicates start of a new or termination of a broken cycle.

95 LPC_AD2 LPC Multiplexed Command, Address and Data line 2

96 LPC_DRQ0* LPC Encoded DMA/Bus Master Request line 0

97 LPC_AD3 LPC Multiplexed Command, Address and Data line 3

98 LPC_DRQ1* LPC Encoded DMA/Bus Master Request line 1

99 GND Ground

100 GND Ground

Notes: The shaded area denotes power or ground. The signals marked with * = Negative true logic.