Chapter 3 Hardware

52 Reference Manual XTX 820

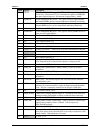

Pin # Signal Description

22 I

2

DAT I

2

C Data – This data line supports the I

2

C bus which supports external slave

devices only. The interface I

2

C bus is intended for support of EEPROMs

and other simple I/O-devices. The data rate is approximate 1-10kHz.

23 SMBCLK System Management Bus Clock – This signal is used to support internal

and external SMBus devices, such as temperature and battery monitoring.

24 SMBDATA System Management Bus Data – This signal is used to support internal and

external SMBus devices, such as temperature and battery monitoring.

25 NC Not Connected (SIDE_CS3*)

26 SMBALRT* System Management Bus Alert – This signal is used by SMBus devices to

signal an event on the SM Bus.

27 NC Not Connected (SIDE_CS1*)

28 NC Not Connected (DASP_S)

29 NC Not Connected (SIDE_A2)

30 PIDE_CS3* Primary Chip Select 3 – Selects host-accessible Command Block Register.

31 NC Not Connected (SIDE_A0)

32 PIDE_CS1* Primary Chip Select 1 – Selects host-accessible Command Block Register.

33 GND2

Ground

34 GND4

Ground

35 NC Not Connected (PDIAG_S)

36 PIDE_A2 Primary Drive Address Bus 2 – Used (0 to 2) to indicate which byte in the

ATA command block or control block (register) is being accessed.

37 NC Not Connected (SIDE_A1)

38 PIDE_A0 Primary Drive Address Bus 0 – Refer to PIDE_A2, pin-36, for more

information.

39 NC Not Connected (SIDE_INTRQ)

40 PIDE_A1 Primary Drive Address Bus 1 – Refer to PIDE_A2, pin-36, for more

information.

41 BATLOW*

Battery Low – This external signal to the XTX 820 indicates when the

external battery is low.

42 GPE1*

General Purpose Power Management Event Input 1 – This signal may be

driven low by external circuitry to signal an external power management

event. This pin is commonly connected to the chipset’s LID# input.

43 NC Not Connected (SIDE_AK*)

44 PIDE_INTRQ Primary Drive Interrupt Request (IRQ 14)– Asserted by drive when it has

pending interrupt (PIO transfer of data to or from the drive to the host).

45 NC Not Connected (SIDE_RDY)

46 PIDE_AK* Primary DMA Channel Acknowledge – Used by the host to acknowledge

data has been accepted or data is available. Used in response to

PIDE_DMARQ asserted.

47 NC Not Connected (SIDE_IOR*)

48 PIDE_RDY Primary I/O Channel Ready – When negated extends the host transfer cycle

of any host register access when the drive is not ready to respond to a data

transfer request. High impedance if asserted.

49 VCC2 +5 volts +/-5%