User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Programming Model

Page 100 of 377

gx_02.fm.(1.2)

March 27, 2006

Implementation Notes—The following notes describe the 750GX implementation of integer load instruc-

tions:

• The PowerPC Architecture cautions programmers that some implementations of the architecture might

execute the load half algebraic (lha, lhax) instructions and the load word with update (lbzu, lbzux, lhzu,

lhzux, lhau, lhaux, lwu, lwux) instructions with greater latency than other types of load instructions. This

is not the case for the 750GX. These instructions operate with the same latency as other load instruc-

tions.

• The PowerPC Architecture cautions programmers that some implementations of the architecture might

run the load/store byte-reverse (lhbrx, lbrx, sthbrx, stwbrx) instructions with greater latency than other

types of load/store instructions. This is not the case for the 750GX. These instructions operate with the

same latency as the other load/store instructions.

• The PowerPC Architecture describes some preferred instruction forms for load-and-store multiple instruc-

tions and integer move assist instructions that might perform better than other forms in some implementa-

tions. None of these preferred forms affect instruction performance on the 750GX.

• The PowerPC Architecture defines the load word and reserve indexed (lwarx) and the store word condi-

tional indexed (stwcx.) instructions as a way to update memory atomically. In the 750GX, reservations

are made on behalf of aligned 32-byte sections of the memory address space. Executing lwarx and

stwcx. to a page marked write-through does not cause a DSI exception if the write-through (W) bit is set.

However, as with other memory accesses, DSI exceptions can result for other reasons such as protection

violations or page faults.

• In general, because stwcx. always causes an external bus transaction, it has slightly worse performance

characteristics than normal store operations.

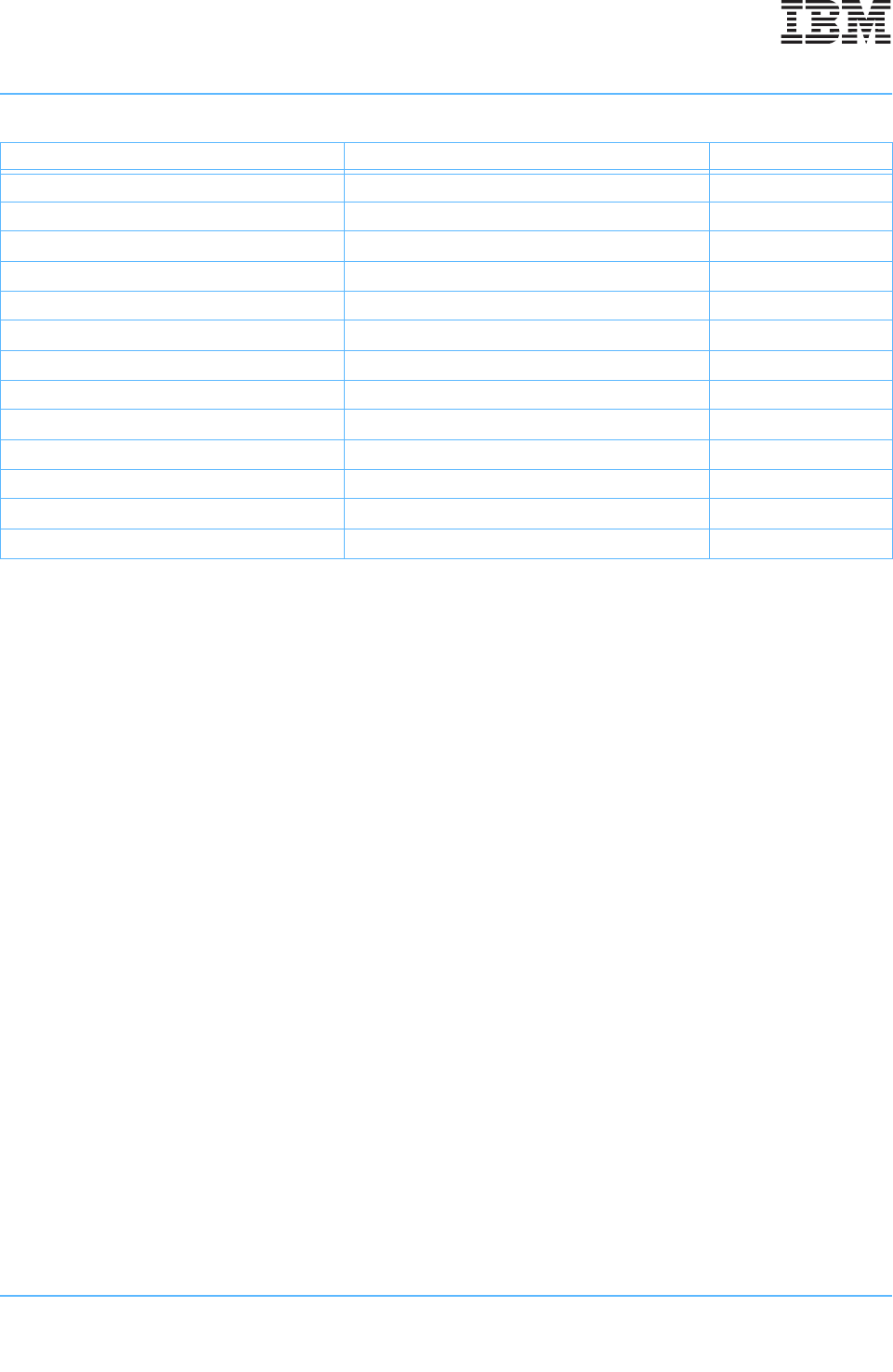

Load Byte and Zero with Update Indexed lbzux rD,rA,rB

Load Half Word and Zero lhz rD,d(rA)

Load Half Word and Zero Indexed lhzx rD,rA,rB

Load Half Word and Zero with Update lhzu rD,d(rA)

Load Half Word and Zero with Update Indexed lhzux rD,rA,rB

Load Half Word Algebraic lha rD,d(rA)

Load Half Word Algebraic Indexed lhax rD,rA,rB

Load Half Word Algebraic with Update lhau rD,d(rA)

Load Half Word Algebraic with Update Indexed lhaux rD,rA,rB

Load Word and Zero lwz rD,d(rA)

Load Word and Zero Indexed lwzx rD,rA,rB

Load Word and Zero with Update lwzu rD,d(rA)

Load Word and Zero with Update Indexed lwzux rD,rA,rB

Table 2-18. Integer Load Instructions (Page 2 of 2)

Name Mnemonic Syntax