User’s Manual

IBM PowerPC 750GX and GL RISC Microprocessor

Exceptions

Page 174 of 377

gx_04.fm.(1.2)

March 27, 2006

Like the external interrupt, a system management interrupt is signaled to the 750GX by the assertion of an

input signal. The system management interrupt signal (SMI) is expected to remain asserted until the interrupt

is taken. If SMI is negated early, recognition of the interrupt request is not guaranteed. After the 750GX

begins execution of the system management interrupt handler, the system can safely negate SMI. After the

assertion of SMI is detected, the 750GX stops dispatching instructions and waits for all pending instructions

to complete. This allows any instructions in progress that need to take an exception to do so before the

system management interrupt is taken.

When a system management interrupt exception is taken, instruction fetching resumes at offset 0x01400

from the base address indicated by MSR[IP].

4.5.16 Thermal-Management Interrupt Exception (0x01700)

A thermal-management interrupt is generated when the junction temperature crosses a threshold

programmed in either THRM1 or THRM2. The exception is enabled by the thermal-management interrupt

enable (TIE) bit of either THRM1 or THRM2, and can be masked by setting MSR[EE].

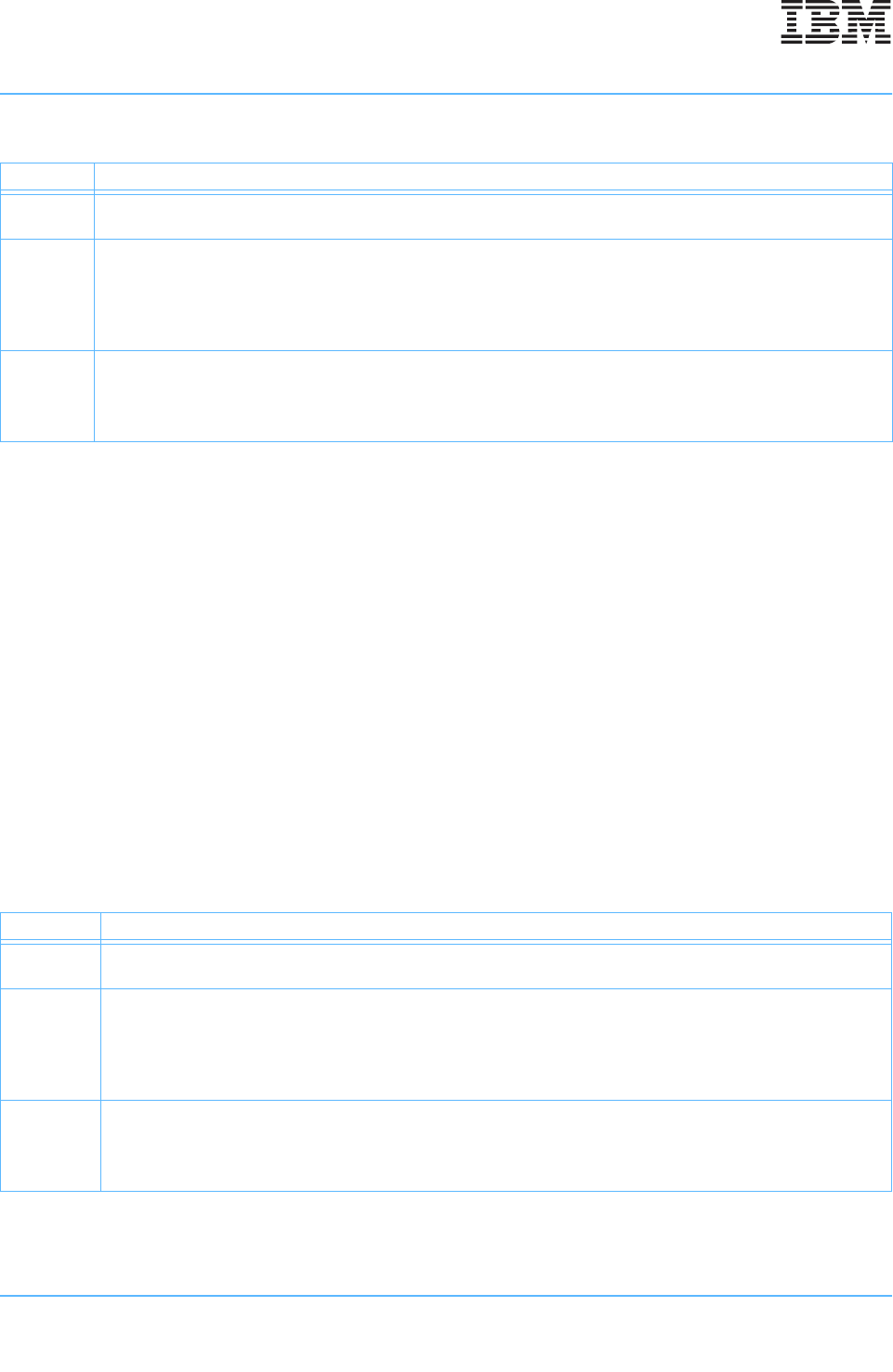

Table 4-13 lists register settings when a thermal-management interrupt exception is taken.

Table 4-12. System Management Interrupt Exception—Register Settings

Register Setting Description

SRR0

Set to the effective address of the instruction that the processor would have attempted to execute next if no exception

conditions were present.

SRR1

0 Loaded with equivalent MSR bits.

1:4 Cleared.

5:9 Loaded with equivalent MSR bits.

10:15 Cleared.

16:31 Loaded with equivalent MSR bits.

MSR

POW 0

ILE —

EE 0

PR 0

FP 0

ME —

FE0 0

SE 0

BE 0

FE1 0

IP —

IR 0

DR 0

PM 0

RI 0

LE Set to value of ILE

Table 4-13. Thermal-Management Interrupt Exception—Register Settings

Register Setting Description

SRR0

Set to the effective address of the instruction that the processor would have attempted to execute next if no exception

conditions were present.

SRR1

0 Loaded with equivalent MSR bits

1:4 Cleared

5:9 Loaded with equivalent MSR bits

10:15 Cleared

16:31 Loaded with equivalent MSR bits

MSR

POW 0

ILE —

EE 0

PR 0

FP 0

ME —

FE0 0

SE 0

BE 0

FE1 0

IP —

IR 0

DR 0

PM 0

RI 0

LE Set to value of ILE