User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Programming Model

Page 72 of 377

gx_02.fm.(1.2)

March 27, 2006

2.1.2.5 Performance-Monitor Registers

This section describes the registers used by the performance monitor, which is described in Chapter 11,

Performance Monitor and System Related Features, on page 349.

Monitor Mode Control Register 0 (MMCR0)

The Monitor Mode Control Register 0 (MMCR0) is a 32-bit SPR provided to specify events to be counted and

recorded. The MMCR0 can be accessed only in supervisor mode. User-level software can read the contents

of MMCR0 by issuing an mfspr instruction to UMMCR0, described in the following section.

This register must be cleared at power up. Reading this register does not change its contents. MMCR0 can

be accessed with mtspr and mfspr using SPR 952.

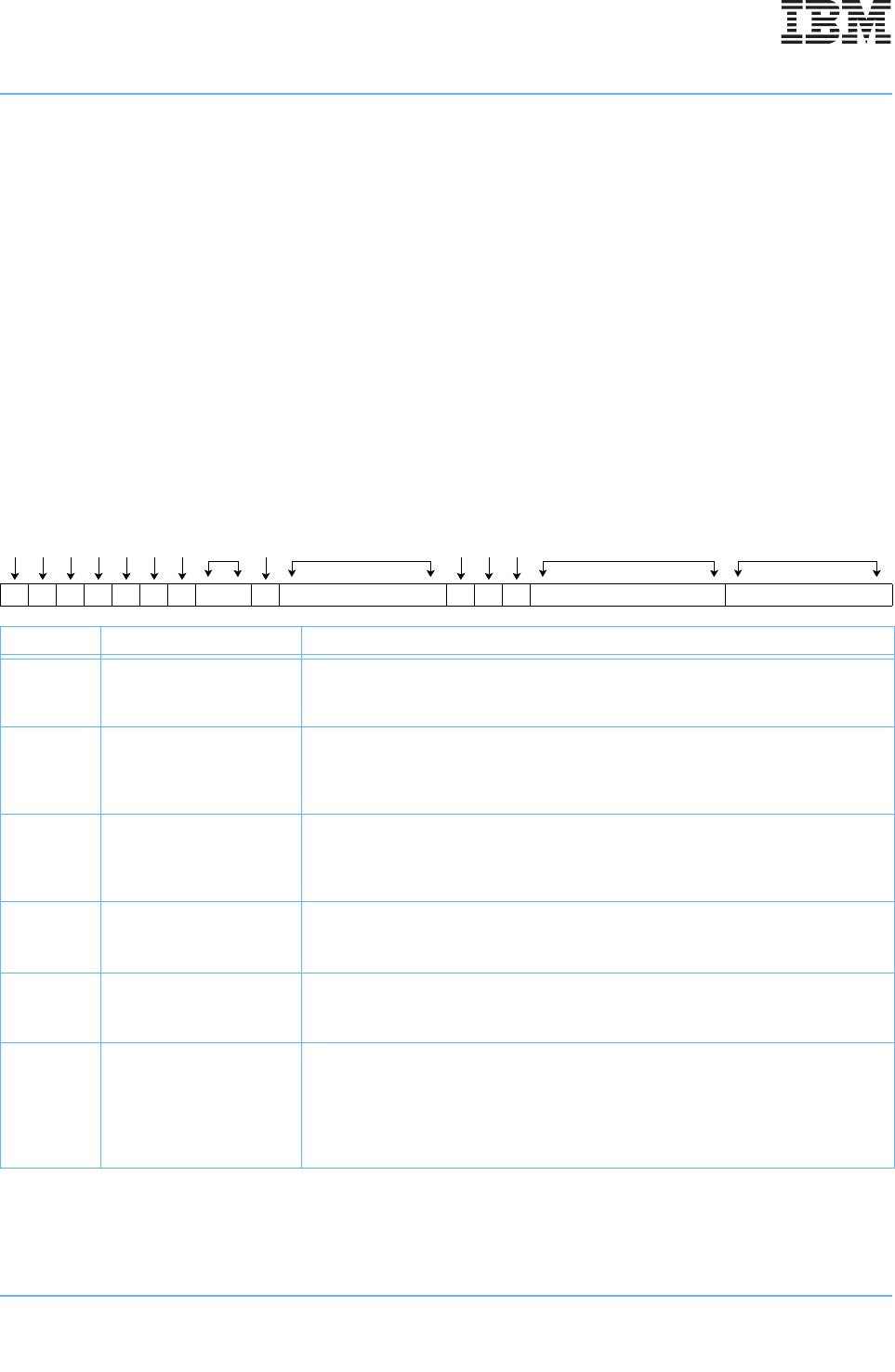

DIS

DP DU

DMS

DMR

ENINT

DISCOUNT

RTCSELECT

INTONBITTRANS

THRESHOLD

PMC1INTCONTROL

PMC2INTCONTROL

PMCTRIGGER

PMC1SELECT PMC2SELECT

012345678910111213141516171819202122232425262728293031

Bits Field Name Description

0 DIS

Disables counting unconditionally.

0 The values of the PMCn counters can be changed by hardware.

1 The values of the PMCn counters cannot be changed by hardware.

1 DP

Disables counting while in supervisor mode.

0 The PMCn counters can be changed by hardware.

1 If the processor is in supervisor mode (MSR[PR] is cleared), the counters are not

changed by hardware.

2 DU

Disables counting while in user mode.

0 The PMCn counters can be changed by hardware.

1 If the processor is in user mode (MSR[PR] is set), the PMCn counters are not

changed by hardware.

3DMS

Disables counting while MSR[PM] is set.

0 The PMCn counters can be changed by hardware.

1 If MSR[PM] is set, the PMCn counters are not changed by hardware.

4DMR

Disables counting while MSR[PM] is zero.

0 The PMCn counters can be changed by hardware.

1 If MSR[PM] is cleared, the PMCn counters are not changed by hardware.

5 ENINT

Enables performance-monitor interrupt signaling.

0 Interrupt signaling is disabled.

1 Interrupt signaling is enabled.

Cleared by hardware when a performance-monitor interrupt is signaled. To re-enable

these interrupt signals, software must set this bit after handling the performance-monitor

interrupt.