User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Programming Model

Page 68 of 377

gx_02.fm.(1.2)

March 27, 2006

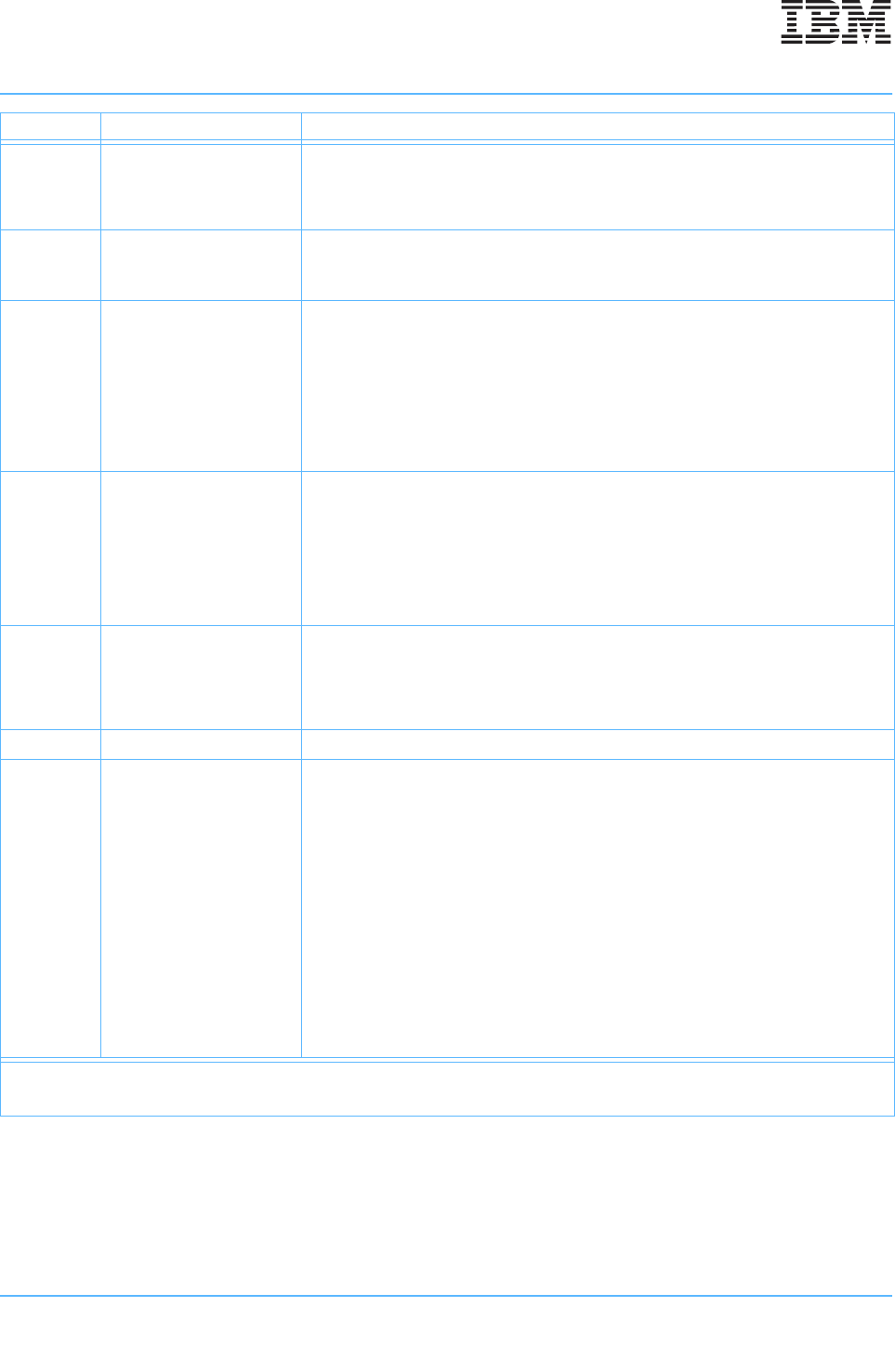

22 SPD

Speculative cache access disable

0 Speculative bus accesses to nonguarded space (G = 0) from both the instruction

and data caches are enabled.

1 Speculative bus accesses to nonguarded space in both caches are disabled.

23 IFEM

Enable M bit on bus for instruction fetches.

0 M bit disabled. Instruction fetches are treated as nonglobal on the bus.

1 Instruction fetches reflect the M bit from the WIM settings.

24 SGE

Store gathering enable

0 Store gathering is disabled.

1 Integer store gathering is performed for write-through to nonguarded space or for

cache-inhibited stores to nonguarded space for 4-byte, word-aligned stores. The

load store unit (LSU) combines stores to form a double word that is sent out on

the 60x bus as a single-beat operation. Stores are gathered only if successive,

eligible stores are queued and pending. Store gathering is performed regardless

of address order or endian mode. The store-gathering feature is enabled by set-

ting the HID0[SGE] bit (bit 24).

25 DCFA

Data-cache flush assist. (Force data cache to ignore invalid sets on miss replacement

selection.)

0 The data-cache flush assist facility is disabled.

1 The miss replacement algorithm ignores invalid entries and follows the replace-

ment sequence defined by the PLRU bits. This reduces the series of uniquely

addressed load or Data Cache Block Zero (dcbz) instructions to eight per set.

The bit should be set just before beginning a cache flush routine, and should be

cleared when the series of instructions completes.

26 BTIC

Branch target instruction-cache enable—used to enable use of the 64-entry branch

instruction cache.

0 The BTIC is disabled, the contents are invalidated, and the BTIC behaves as if it

were empty. New entries cannot be added until the BTIC is enabled.

1 The BTIC is enabled, and new entries can be added.

27 — Not used. Defined as FBIOB on earlier 603-type processors.

28 ABE

Address broadcast enable—controls whether certain address-only operations (such as

cache operations, Enforce In-Order Execution of I/O [eieio], and Synchronization [sync])

are broadcast on the 60x bus.

0 Address-only operations affect only local L1 and L2 caches and are not broad-

cast.

1 Address-only operations are broadcast on the 60x bus. Affected instructions are

eieio, sync, Data Cache Block Invalidate (dcbi), Data Cache Block Flush (dcbf),

and Data Cache Block Store (dcbst). A sync instruction completes only after a

successful broadcast. Execution of eieio causes a broadcast that can be used to

prevent any external devices, such as a bus bridge chip, from store gathering.

Note: A Data Cache Block Set to Zero (dcbz) instruction (with M = 1, coherency

required) always broadcasts on the 60x bus regardless of the setting of this bit. An

Instruction Cache Block Invalidate (icbi) is never broadcast. No cache operations, except

dcbz, are snooped by the 750GX regardless of whether the ABE is set. Bus activity

caused by these instructions results directly from performing the operation on the 750GX

cache.

Bits Field Name Description

1. For additional information, see Section 11.9, Checkstops, on page 361.

2. For additional information about power-saving modes, see

Table 10-2, HID0 Power Saving Mode Bit Settings, on page 337.