User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Programming Model

Page 64 of 377

gx_02.fm.(1.2)

March 27, 2006

2.1.2 PowerPC 750GX-Specific Registers

This section describes registers that are defined for the 750GX but are not included in the PowerPC Architec-

ture.

2.1.2.1 Instruction Address Breakpoint Register (IABR)

The Instruction Address Breakpoint Register (IABR) supports the instruction address breakpoint exception.

When this exception is enabled, instruction fetch addresses are compared with an effective address stored in

the IABR. If the word specified in the IABR is fetched, the instruction breakpoint handler is invoked. The

instruction that triggers the breakpoint does not execute before the handler is invoked. For more information,

see Section 4.5.14, Instruction Address Breakpoint Exception (0x01300), on page 173. The IABR can be

accessed with mtspr and mfspr using the SPR 1010.

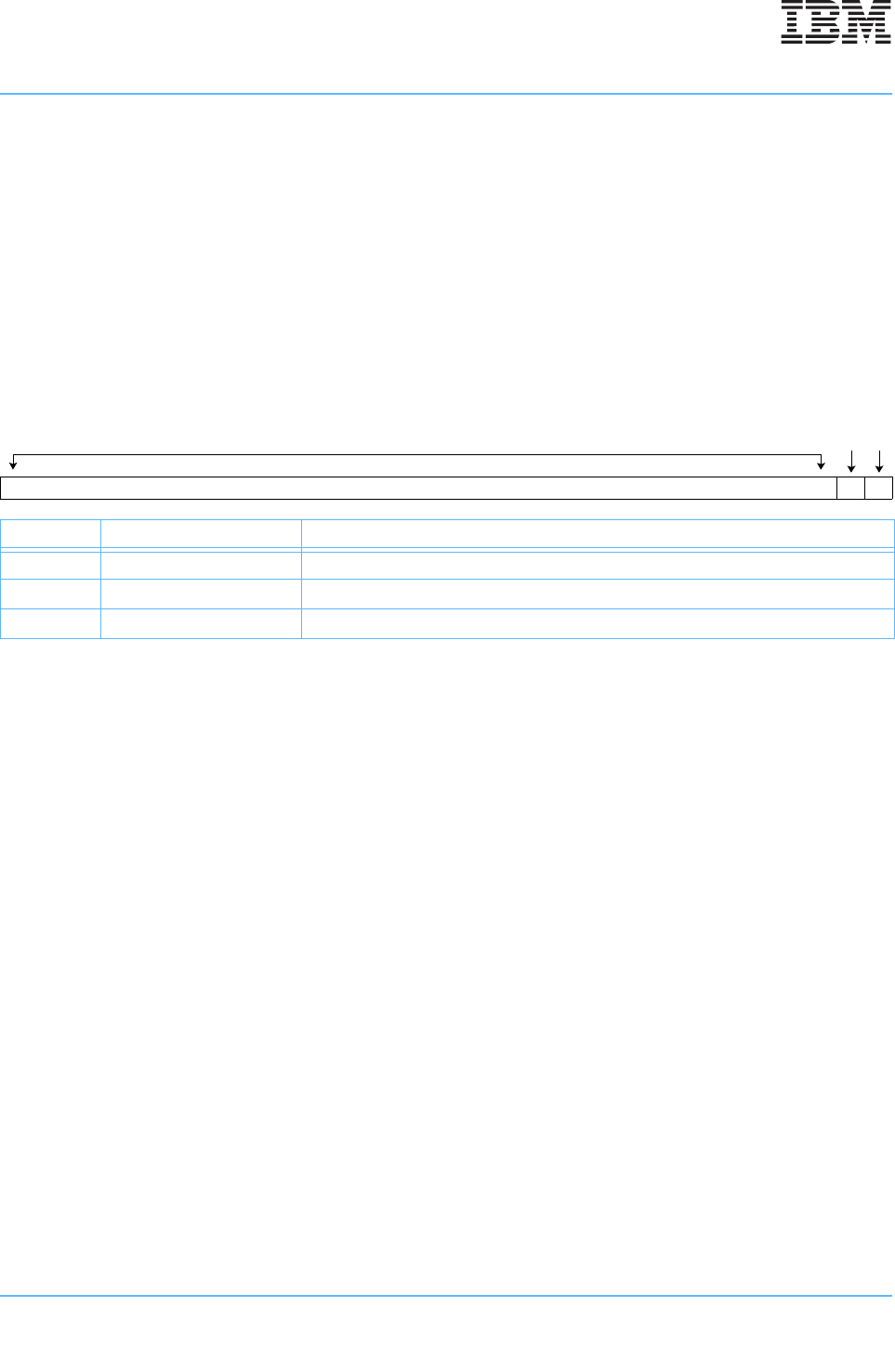

Address BE TE

012345678910111213141516171819202122232425262728293031

Bits Field Name Description

0:29 Address Word address to be compared.

30 BE Breakpoint enabled. Setting this bit indicates that breakpoint checking is to be done.

31 TE Translation enabled. An IABR match is signaled if this bit matches MSR[IR].